| 推挽输出、开漏输出、上拉和下拉电阻总结 | 您所在的位置:网站首页 › fpga开漏输出 › 推挽输出、开漏输出、上拉和下拉电阻总结 |

推挽输出、开漏输出、上拉和下拉电阻总结

|

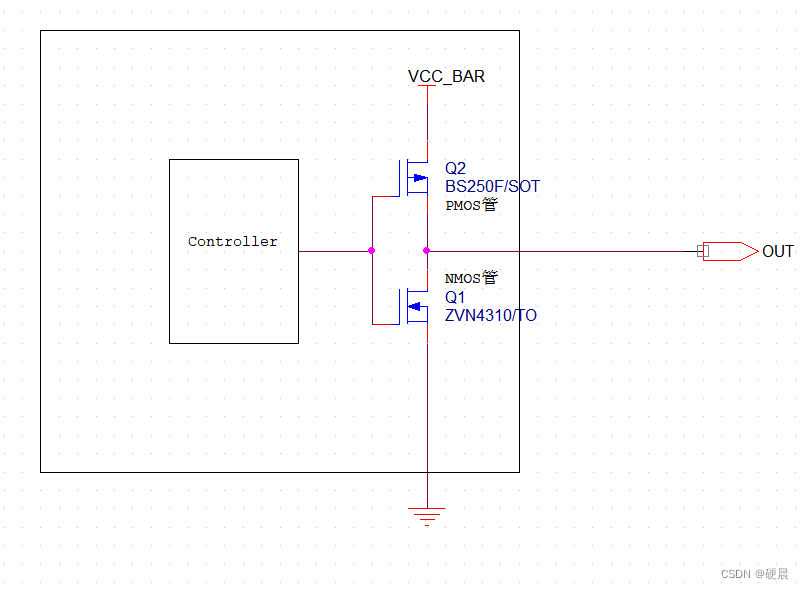

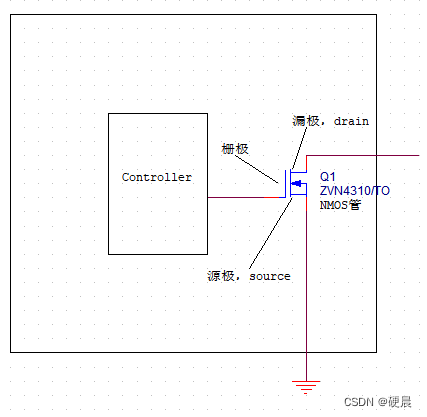

提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档 文章目录 前言一、开漏是什么?上拉电阻下拉电阻 二、推挽是什么?总结 前言此文章是为了共同进步,如有错误请联系更正 开漏输出和推挽输出是模电中很基础的一部分,但很多做嵌入式软件的同学对此硬件基本原理不是很熟悉,所以写此文章,一方面自己巩固与一下。另一方面,帮做纯软件的同学讲解一下(尤其我女朋友😂)。 一、开漏是什么?开漏可能有些人觉得陌生,但是对OD一定很熟悉,比如 GPIO_Mode_Out_OD 这是STM32的GPIO的开漏输出模式。 没错,OD就是open drain,开漏的意思。就是漏极开放的意思。 我用cadence简单画了个图: 相当于MCU局部的IO口

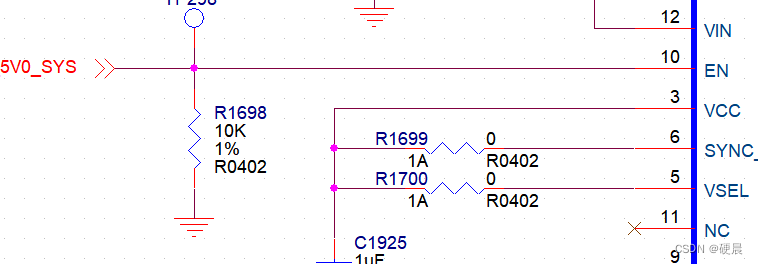

=图1= 然后对于做纯软件的同学,NMOS和PMOS的区别,然后栅极源极漏极这些感兴趣可以补一下,图里面我已经写出来,可以看到漏极是开放的。 知道Nmos是栅极为高电平时导通,低电平不导通即可 上拉电阻图1是没有接上拉电阻的MCU的局部简化图。可以看到 当controller写入1时,mos导通,相当于导线,相当于漏极那边连的东西直接接地,所以是输出低电平。 当controller写入0时,mos不导通,外面悬空了,相当于漏极那边连的东西是未知的,可能随负载的电平而变化,所以不能确定电平。 但是接上拉电阻后: 下拉一般就是把电压拉到GND。笔者目前对下拉的经验及认知就是比如: 芯片的使能pin接地,这样相当于规定初始状态为不使能,然后接入MCU来控制。如下图: 同样地,在STM32的GPIO输出模式中,应该很熟悉这个: GPIO_Mode_Out_PP Push-Pull,就是推挽,简称PP。下面用图像说明一下PP: 用Circuit JS做了个动图 可以很明显的看出,推电流和挽电流的意思是啥,一个从发射极输出电流,一个从发射极进来电流,“推”电流和把电流“挽”过来,是不是很形象 上面这个动图是两个三极管,但一般芯片的GPIO口是两个mos管,如下图: 上面是PMOS管,下面是NMOS管,如上图这样连接就是推挽电路。 注意PMOS管导通电压是低电平,NMOS是高电平导通,下面讲解会用到这点 当controller写入1时,NMOS导通,PMOS截至,相当于漏极那边连的东西直接接地,所以是输出低电平。 当controller写入0时,NMOS截至,PMOS导通,相当于漏极那边连的VCC,所以输出高电平。 所以推挽输出能直接输出高低电平 总结后续不定期进行补充,欢迎大家一起讨论交流! |

【本文地址】

当controller写入1时,mos导通,相当于导线,vcc、电阻和地形成回路,所以是OUT端口输出低电平。 当controller写入0时,mos不导通,vcc、电阻和地形成回路,所以是OUT端口被拉到VCC,输出高电平。

当controller写入1时,mos导通,相当于导线,vcc、电阻和地形成回路,所以是OUT端口输出低电平。 当controller写入0时,mos不导通,vcc、电阻和地形成回路,所以是OUT端口被拉到VCC,输出高电平。 相当于EN直接和电阻和GND相连,默认就是低电平了,然后接入别的MCU来控制使能。

相当于EN直接和电阻和GND相连,默认就是低电平了,然后接入别的MCU来控制使能。