| 数字IC笔面基础之触发器 | 您所在的位置:网站首页 › ff的意思是什么意思啊 › 数字IC笔面基础之触发器 |

数字IC笔面基础之触发器

|

数字IC笔面基础之触发器

写在前面的话关键点:

D触发器基本正边沿触发D触发器异步复位D触发器带清零和置一的D触发器

T触发器JK触发器总结

写在前面的话

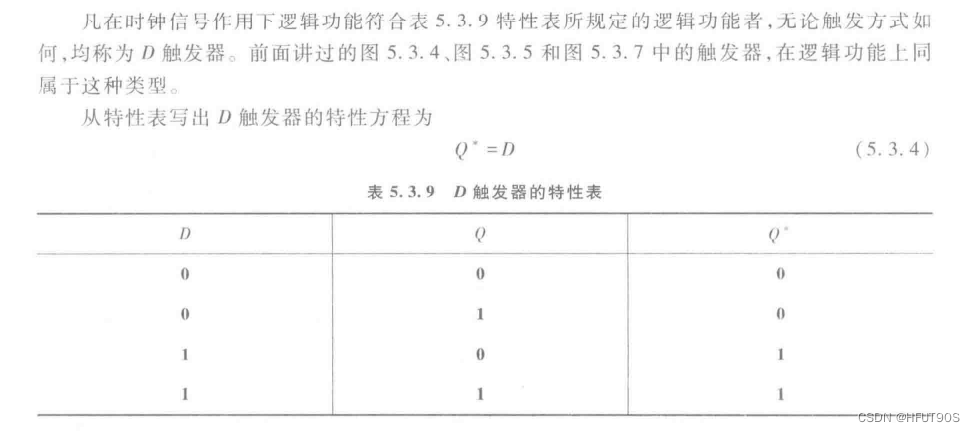

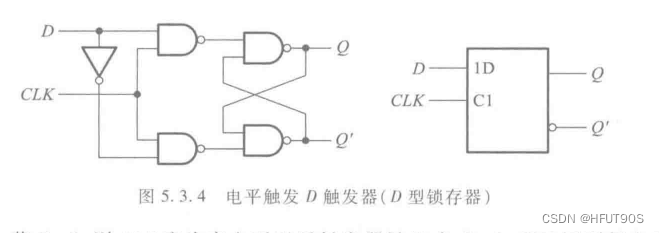

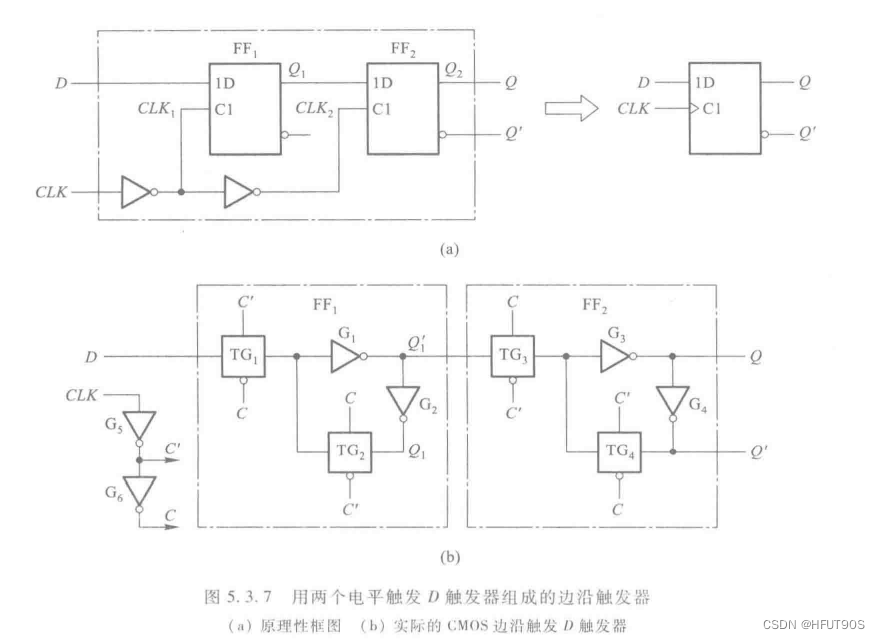

触发器是数字IC最基础的知识点,区别于锁存器,触发器是只有在时钟信号触发时才能动作的存储单元,每个触发器可以存储1位二值信号。触发器有两个基本特点: (1)具有自行保持稳定状态,包含逻辑0和逻辑1。 (2)可以根据输入信号置为1或0状态。 关键点:笔面时常考的知识点是区分锁存器(Latch)和触发器(Flip-Flop),了解哪些代码风格可能会被综合成Latch,尽量避免。(在实际项目中有时需要故意生成Latch) 锁存器(Latch):电平触发,数据存储取决于信号的电平值。电平有效时,输出信号被锁存。 锁存器如下: 触发器(Flip-Flop):边沿触发,数据存储取决于信号的上升沿或下降沿。 触发器如下: 锁存器和触发器优缺点: 锁存器优点: (1)面积比触发器小 门电路时构建组合逻辑电路的基础,而锁存器和触发器是构成时序逻辑电路的基础。 晶体管>>门电路>>锁存器>>触发器 Latch完成同一个功能所需的门较触发器要少,在ASIC中用的比较多。 (2)速度比触发器快 用来地址锁存是很合适,不过一定要保证所有的Latch信号源的质量,锁存器在CPU设计中很常见,锁存器使得CPU的速度比外部IO部件逻辑快很多。 锁存器缺点: (1)电平触发,非同步设计,受布线延迟影响较大,很难保证输出没有毛刺。 (2)Latch将静态时序分析变得极其复杂。 触发器优点: (1)边沿触发,同步设计,不容易受毛刺的影响。 (2)时序分析简单 触发器缺点: (1)面积比Latch大,消耗的门电路比latch多。 (2)过多的触发器使得数据逻辑变得复杂。 D触发器D触发器的次态取决于触发之前D端口的状态。 |

【本文地址】

寄存器(Register): Verilog中用来暂时存放数据的变量。变量被声明为寄存器时,可能被综合成Latch或者Fliop-Flop。

寄存器(Register): Verilog中用来暂时存放数据的变量。变量被声明为寄存器时,可能被综合成Latch或者Fliop-Flop。