| mini2440开发板一些硬件介绍(PTC、定时器、串口、中断控制器、SDROAM、Norflash、Nandflash) | 您所在的位置:网站首页 › dsp开发板介绍 › mini2440开发板一些硬件介绍(PTC、定时器、串口、中断控制器、SDROAM、Norflash、Nandflash) |

mini2440开发板一些硬件介绍(PTC、定时器、串口、中断控制器、SDROAM、Norflash、Nandflash)

|

什么是mini2440?

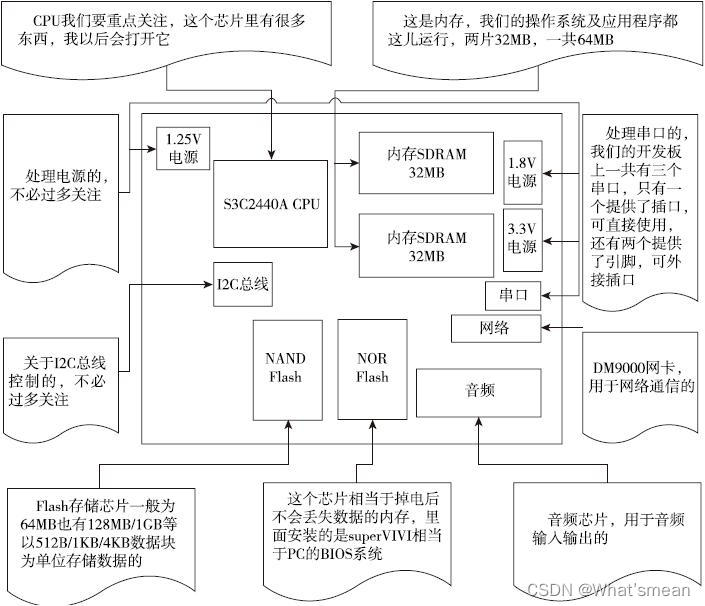

mini2440开发板,是友善之臂公司基于三星公司的S3C2440A芯片,并结合了一系列的外围组件开发出来的一款嵌入式开发板。组件非常丰富,性能不错,也很常用,非常适合嵌入式系统的入门学习。如图为其逻辑视图:

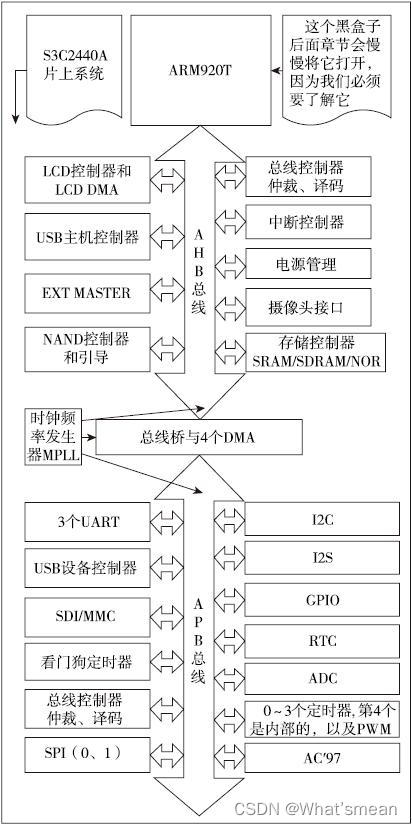

S3C2440A基于ARM920T核心,ARM920T核心才是我们通常说的CPU、处理器,它支持16/32位精简指令集。它还实现了内存管理单元MMU。S3C2440A还提供了丰富的内部设备,为了组织和连接这些内部设备,它内部采用了先进的微控制总线构架AMBA。为了提高程序的执行速度,S3C2440A还采用了哈佛架构(高速缓冲体系结构),这一结构具有独立的16KB指令,高速缓存和16KB数据高速缓存,每个都是由具有8字长的行(line)组成的。如图为逻辑视图:

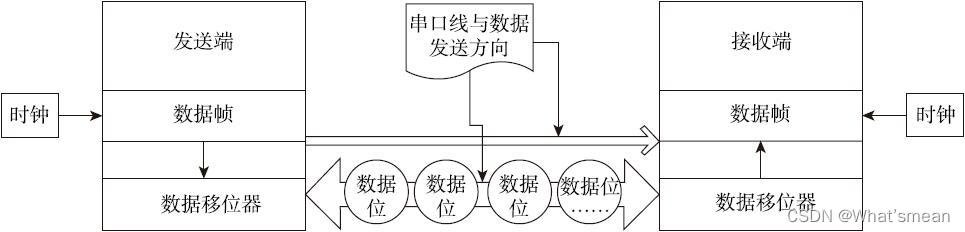

1.RTC 处理自然时间的,可以用备用电池供电维持时间。 具体功能: 1)时间:年、月、日、星期、时、分和秒,支持CPU以BCD数据的方式读写。 2)闰年发生器:支持实现和识别哪年是闰年。 3)闹钟功能:能产生闹钟定时中断或者从省电模式下唤醒开发板。 4)已经解决2000年是闰年的问题。 5)支持独立电源引脚也就是用备用电池供电的功能。 6)支持时钟节拍中断,如一秒钟内产生固定次数的中断。 2.定时器定时器最常用的一个情景:我们让定时器每隔1ms产生一次中断,然后在中断处理程序中检查一个进程已经运行了多长时间,分配给这个进程的时间它是否已经用完,如果已经用完,就调度其他进程运行。如果没有定时器,我们在应用软件中写入一个死循环代码,操作系统立马就会被这个应用软件锁死,因为系统已经没有任何手段从这个应用程序手里夺回CPU的使用权了。 S3C2440A芯片内部有5个定时器,可以用于处理间隔时间,比如,一个进程要等待5ms后去访问硬件等。 其中定时器0、1、2、3具有脉宽调制功能。定时器4是一个无输出引脚的内部定时器。定时器0还包含用于大电流驱动的死区发生器。 这5个定时器所有的特性如下: 1)5个16位定时器。 2)2个8位预分频器和两个4位分频器。 3)可编程输出波形的占空比控制。 4)自动重载模式或单稳态脉冲模式。 5)死区发生。 3.串口用于和其他设备通信或者传输数据,比如,连接PC输出信息,并且S3C2440A芯片内部有三个相同的串口硬件。 S3C2440A中每个串口单元都是可以基于中断或基于DMA模式操作的。S3C2440A的串口包括了可编程波特率,红外发送/接收,插入1个或2个停止位,5位、6位、7位或8位的数据宽度以及奇偶校验。每个串口包含一个波特率发生器、发送器、接收器和一个控制单元。每个串口发送数据是可编程的。由1个起始位、5~8个数据位、1个可选奇偶校验位以及1~2个停止位组成的帧,是由行控制寄存器指定的。发送器也可以产生单帧发送期间强制串行输出为逻辑0状态的断点状态。串口设备通信过程:

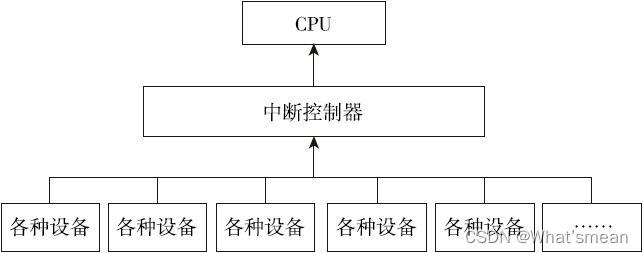

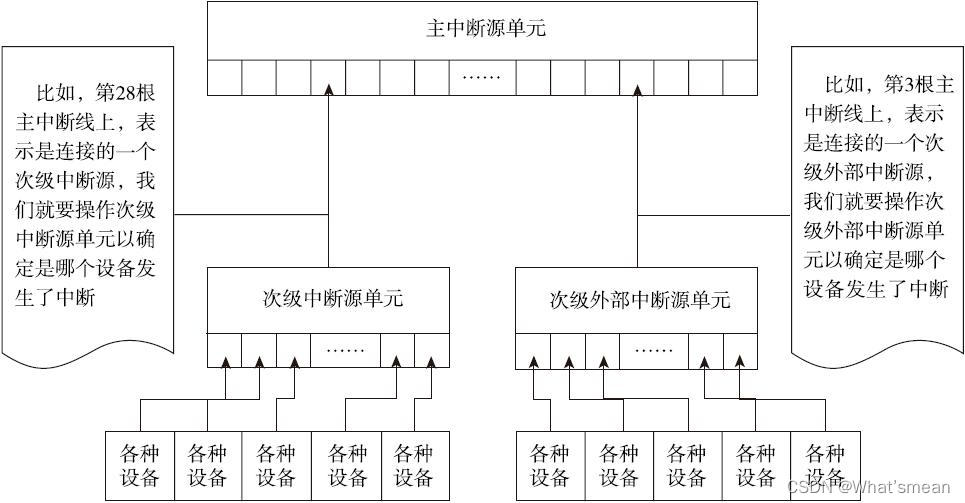

4.中断控制器 存在于S3C2440A芯片内部,是设备和CPU通信的重要机制,支持多达60个设备中断源,同时也支持中断优先级,哪些设备的中断要尽快发送给CPU内核进行处理,也可以屏蔽某个设备的中断信号。

S3C2440A中的中断控制器采用了二级中断源,就是在一级中断的几根中断信号线上连接几个设备的中断信号线。所以当中断发生时,我们就不能单纯地认为是一个设备发生了中断,而是要进一步根据次级中断的相关信息确定是哪个设备发生了中断,如图

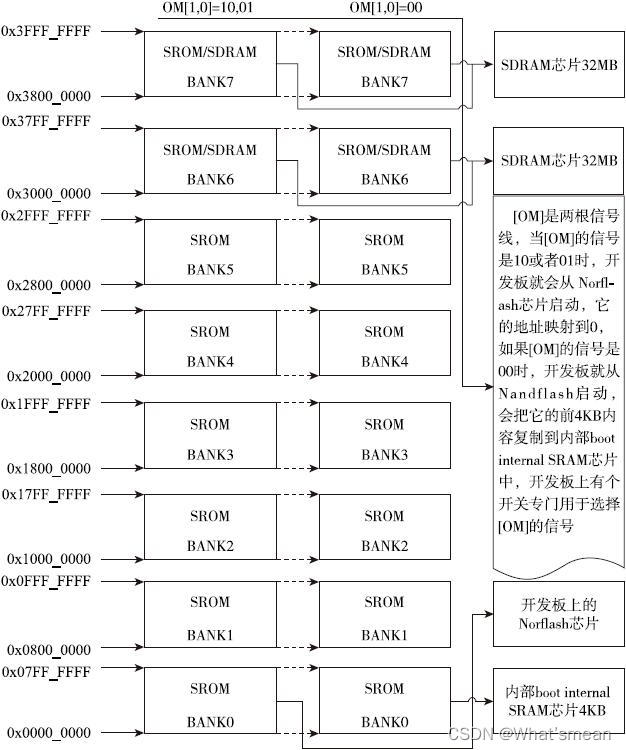

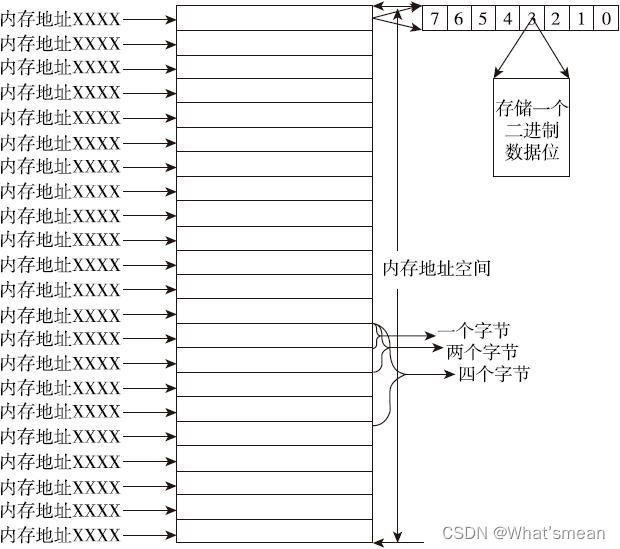

常说的内存,mini2440开发板用了两片32MBSDRAM芯片并接在一起,一共64MB,SDRAM开始的物理地址是0x30000000。操作系统内核和各个应用软件都是放在这个里面运行的。 S3C2440A芯片内的存储器控制器包含以下特性: 1)可通过软件选择大端、小端。 2)总共8个存储器Bank,每个Bank有128MB,总共1GB地址空间。 3)除了Bank0(16/32位),其他全部Bank都可编程访问宽度(8/16/32位)。 4)6个存储器Bank为ROM、SRAM等。其余2个存储器Bank为ROM、SRAM、SDRAM等。 5)7个固定的存储器Bank起始地址,1个可变的存储器Bank起始地址,并且Bank大小可编程。 6)所有存储器Bank的访问周期可编程。 7)支持外部等待扩展总线周期。 8)支持SDRAM自刷新和掉电模式。 S3C2440A的存储地址空间

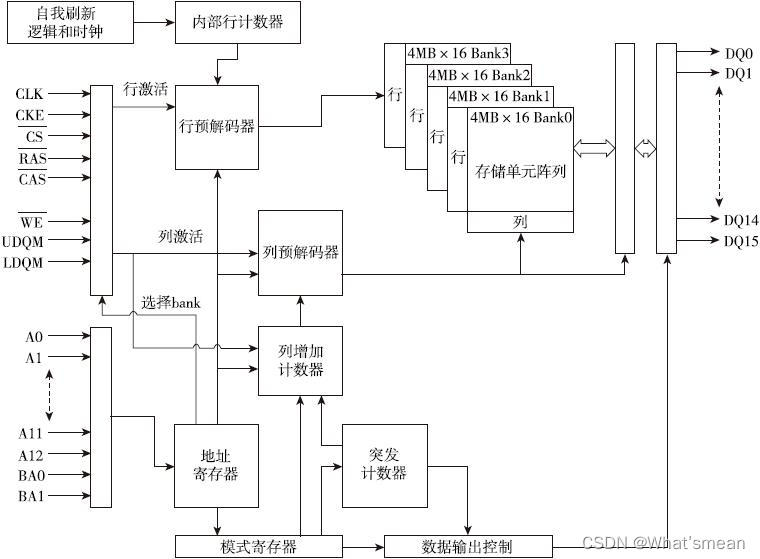

SDRAM芯片结构

内存逻辑视图

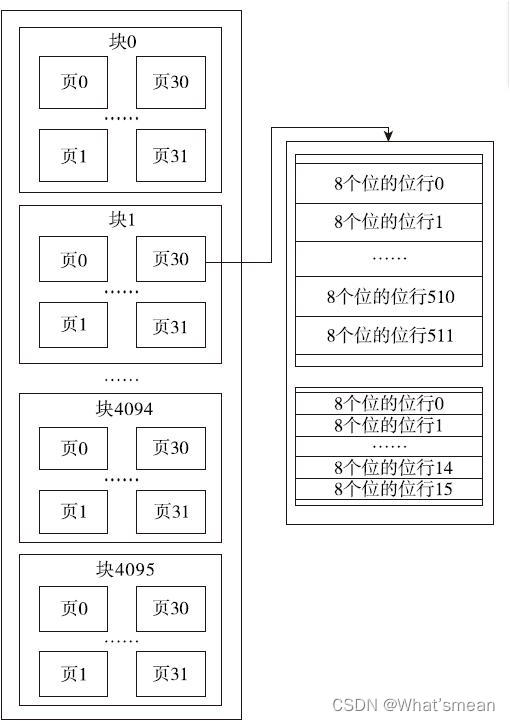

Flash存储器称为闪存,它结合了ROM和RAM的特点,不仅具备电子可擦除、可编程的特点,还可以快速读写数据,而且数据不会因为断电而丢失。这种特性使它可以用于U盘、MP3、智能手机等众多移动智能设备上。 就像是掉电不会丢失数据的内存,支持在其上运行程序。mini2440开发板上有2MB的Norflash芯片,连接在S3C2440A芯片的存储控制器的Bank0上,并能通过跳线开关控制。这个芯片里烧写了一个叫superVIVI的开发板引导程序,相当于PC上的BIOS程序,它负责初始化开发板的时钟和SDRAM等其他设备,然后加载操作系统内核。 mini2440开发板上的Norflash芯片特性如下: 1)有22根地址信号线和16根数据信号线。2)掉电不会丢失数据。3)支持“片上运行”。 7.Nandflash它需要专门设计的控制器来进行读写,一次读写最少是1页,1页最少是528B,512B数据加16B的校验信息,32页组成一个块。我们的开发板上这个芯片是64MB。可以用于操作系统构建文件系统,在其上存放用户数据、应用软件、操作系统等。它也支持系统引导,S3C2440A芯片自动把它的前4KB空间的数据读到一个内部4KB的SRAM中,把那个SRAM的首地址映射为0,S3C2440A芯片内部的CPU内核就从内部4KB的SRAM中开始运行了。 Nandflash芯片的数据是以位的方式保存在存储单元中的,一般来说,一个存储单元中只能存储一个位。这些存储单元以8个或者16个为单位,连接成位行,这些位行会再组成页,这些页面会再组成块。Nandflash芯片有多种结构,其中K9F1208芯片是这样的:每页528B,其中512B用于存放数据,还有16B存放这个页面的数据的校验信息,每32个页面形成一个块,块大小为32×528B。具体一片Flash上有多少个块是根据需要决定的。K9F1208的Nandflash芯片具有4096个块,故总容量为4096×(32×528B)一共是66MB,但是其中的2MB是用来保存ECC校验码等额外数据的,故实际中可使用的空间为64MB,如图

Nandflash芯片以页为单位读写数据,所以一次读写最少为512B的数据,不能像Norflash芯片一样可以以字为单位读写数据。而Nandflash芯片是以块为单位擦除数据的。按照这样的组织方式可以形成所谓的三类地址: 1)列地址。 2)页地址。 3)块地址。 由于Nandflash芯片的工艺不能保证存储单元在其生命周期中保持性能的可靠,所以在Nandflash芯片的生产及使用过程中会产生坏块。为了检测其可靠性,在应用Nandflash芯片的系统中一般都会采用一定的坏区管理策略,而管理坏区的前提是能比较可靠地进行坏区检测。如果操作时序和电路稳定性不存在问题,Nandflash芯片出错的时候一般不会造成整个块或页面不能读取或全部出错,而是整个页面(如512B)中只有一位或几位出错。对数据的校验常用的有奇偶校验、CRC校验等,而在Nandflash芯片处理中,一般使用一种比较专业的ECC校验。ECC能纠正单比特错误和检测双比特错误,而且计算速度很快 摘自《深度探索嵌入式操作系统:从零开始设计、架构和开发 (Linux/Unix技术丛书)》 |

【本文地址】