| 简易DDS信号发生器的设计与验证 | 您所在的位置:网站首页 › dds信号发生器的设计 › 简易DDS信号发生器的设计与验证 |

简易DDS信号发生器的设计与验证

|

1.原理

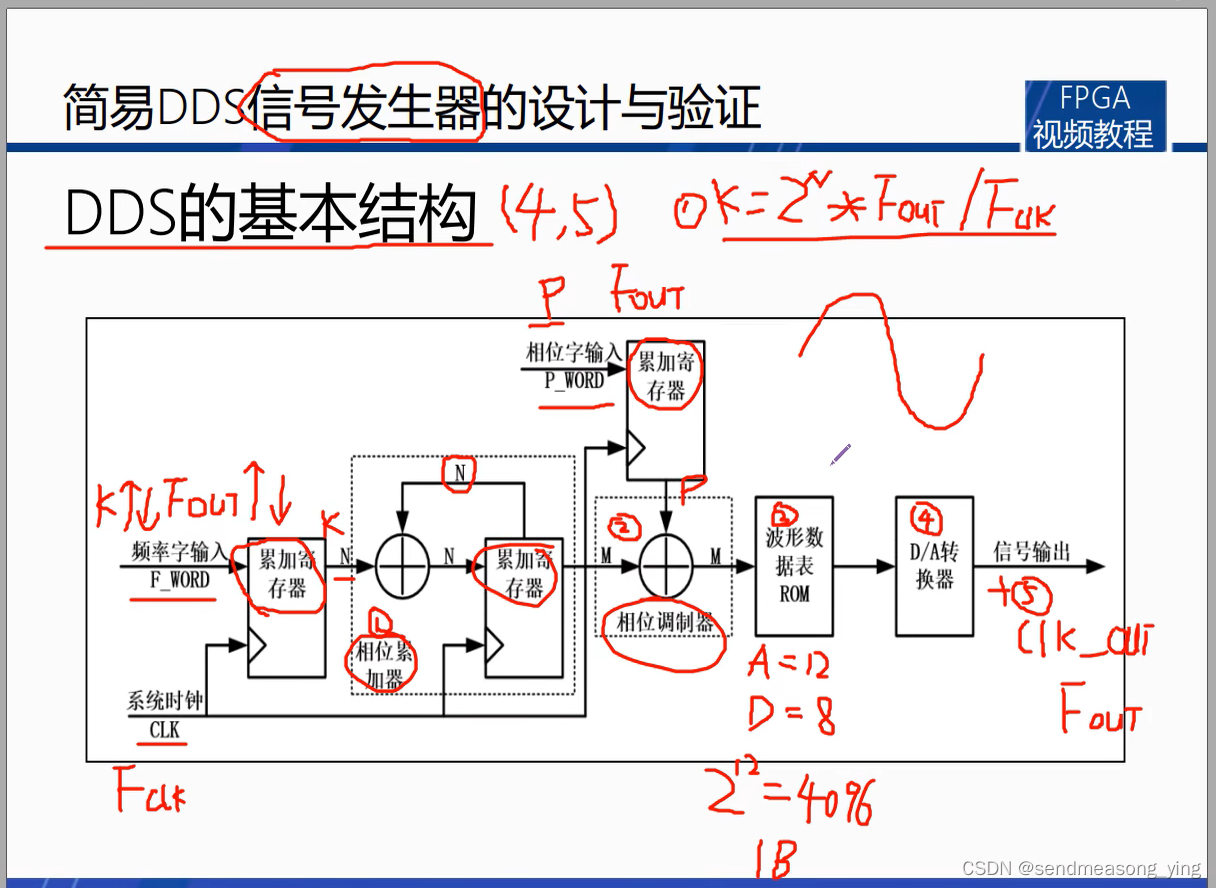

相位累加器:N表示K值位宽。K=2^N*Fout/Fclk。并且在输入相位累加器之前还进行了数据寄存,表示K值在变化的时候,不会影响相位累加器的工作。 相位调制器:寄存器的作用一样的,防止P变化影响相位调制器的正常工作。 波形数据表ROM会存储要显示的完整周期的信号。比如完整周期的正弦波信号,假如地址位宽是12位宽,数据位宽是8位宽,那么就表示有2^12=4096个地址,每个地址可以存储1B数据。对正弦波信号进行完整的存储就是沿着横轴进行等间隔采样4096次,每次 采集的信号幅值用1个字节来表示。最大值是255,最小值是0。每个存储单元都写入一个幅值,这样就把完整的正弦波信号写入到波形数据表ROM当中。然后以相位调制器传入的数据,作为ROM的读地址,然后将地址对应的幅值以数字量的形式输出。 D/A转换器将数字幅值数字量转换成模拟量,就得到了输出信号。 如果有第5部分的话,就将输出信号通过一个低通滤波器,再输出。

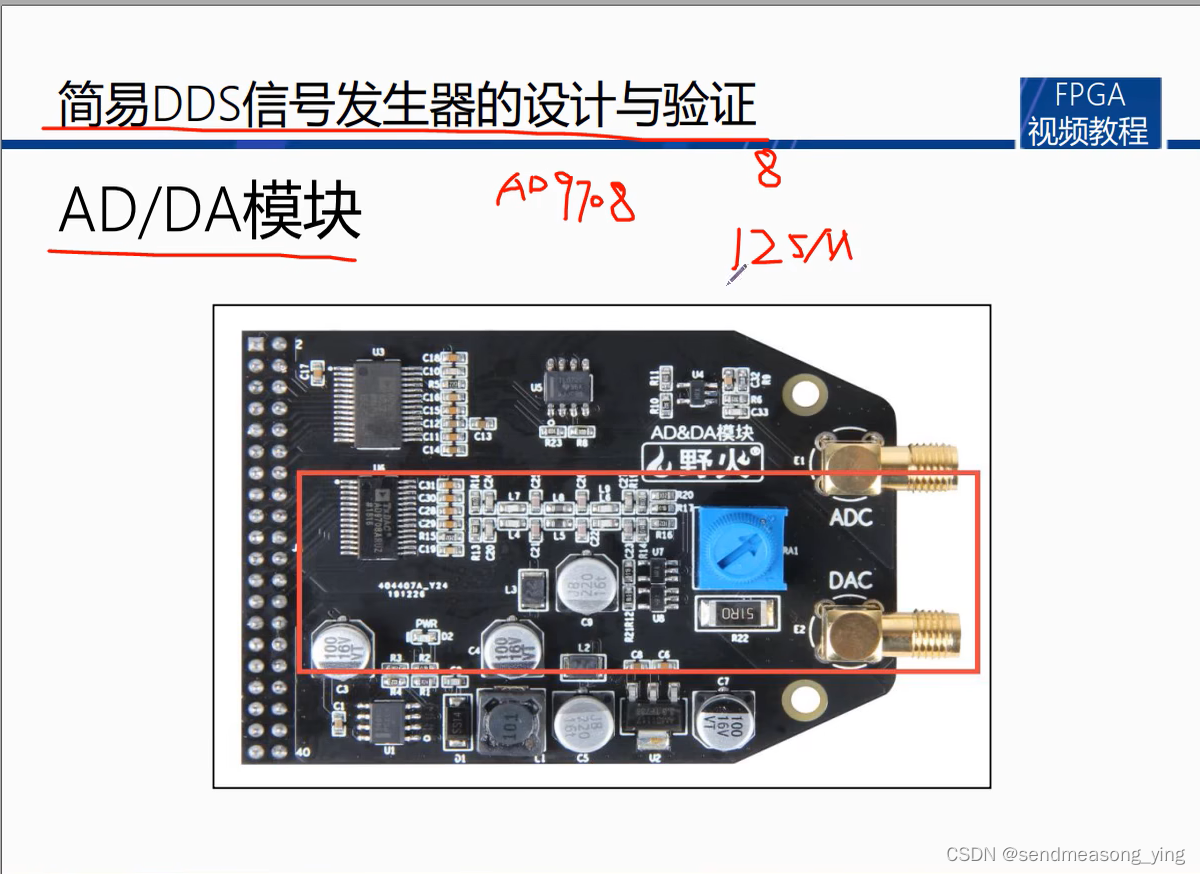

当K等于1时(K是不为0的整数),得到的输出时钟的频率是最小的,得出的Fout是DDS的最小分辨率。K值越大输出时钟的频率越大,但K也不是无限大的,根据采样定理,KM,如图,把N的高8位传给M,也就是并不是每个系统时钟都会对ROM读地址进行一次更新,而是多个时钟周期进行读地址更新,能保证相位累加器溢出时,从正弦ROM表中刚好读取的时整个正弦周期的采样点。相位累加器每计数2^N次对应一个正弦周期,相位累加器一秒钟计数的频率是系统时钟的频率,如果K等于1,输出的时钟就是频率的分辨率,控制K值增加,相位累加器溢出的值就会增加,对应的clk_out的频率就会变为K倍频率分辨率。这样就实现了频率的调节。 举个例子:M=12,D=8,N=32,那么只把N的高12位传给相位调制器,当K等于1,N的低20位每个时钟周期就加1,直到低20位全都为111...111。此时需要进位,把进位就传给M,此时低为又开始从0计数到20位都为1。ROM地址开始等于0,就是把0地址的数据读取2^20次。完成读取之后会向前进位,将1地址,读取2^20次,依次读取,ROM中4096个地址,每个地址都会读取2^20次。输出的频率应该是1/2^20,周期被扩大了2^20倍,当K=100,低20位的数据每次增加100,低20位溢出的时间会比K=1时快100倍,ROM当中一个地址读的次数就是2^20/100次,这时输出的频率就是K=1时输出频率的100倍 利用外部的AD/DA板卡,设计并实现一个简易的DDS信号发生器,使用按键切换正弦波、锯齿波、方波、三角波四种波形的输出。频率相位可以在代码中调节。FPGA实现的是波形数据表ROM及其之间的部分。

最终输出有改动,在输出时钟前加了一个反相器

|

【本文地址】