| XIlinx MIG 控制DDR3 SO | 您所在的位置:网站首页 › ddr内存金手指数 › XIlinx MIG 控制DDR3 SO |

XIlinx MIG 控制DDR3 SO

|

目录

1 内存条上标识的含义1.1 内存条标识1.2 颗粒标识

2 204-pin SO-DIMM 规范2.1 找到本卡在规范中的具体分类2.2 找到本分类对应的引脚定义与连接

3 找到颗粒的关键时序参数4 参考资料

调试DDR3 SO-DIMM 陆陆续续花了好几天,其中的过程比较坎坷。为了避免后面调试的朋友再次踩坑,决定从拿到板子和内存条开始到调试成功中的一些步骤线性的记录下来。 1 内存条上标识的含义拿到一块内存条,让我们用FPGA去控制,可能一开始挺茫然的。以我使用的内存条型号为例,先观察外观:

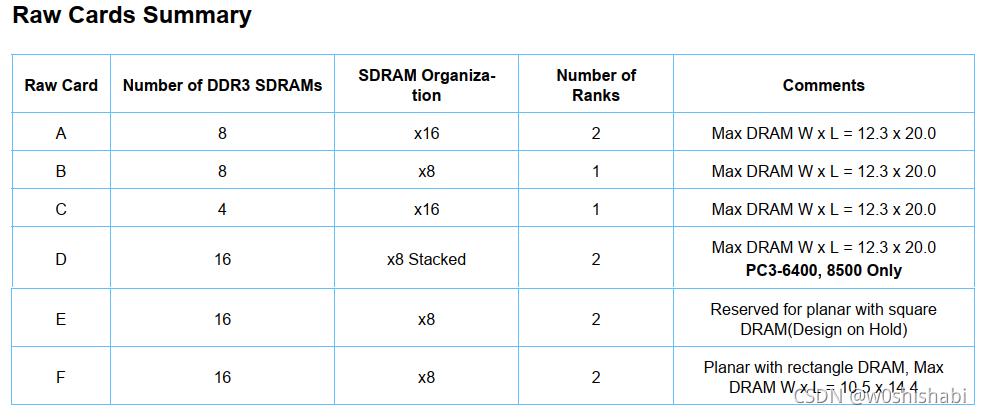

正面标签写了:4GB 1Rx8 PC3L - 12800S - 11 - 11 - B2 看看板卡原理图内存条插槽几个引脚,不同引脚数对应的规范不一样。这是"204-Pin DDR3 SDRAM Unbuffered SO-DIMM Design Specification"规定的 DDR3 “End-User” DIMM类型统一的标签格式:ggggg eRxff PC3-wwwwwm-aa-bb-ccd ggggg: 模块总容量,以字节为单位 256MB, 512MB, 1GB, 2GB, 4GB等等。 eR: 安装的颗粒排列数(rank) 1R: 1rank DDR3 SDRAM2R: 2rank4R: 4rank xff: 内存条上单个DDR3 SDRAM颗粒的数据位宽(也叫Device organization) x4: x4 organization, 即4位x8: x8 organizationx16: x16 organization wwwww: 带宽,单位为MB/s,对于数据总线64bit,这个也可认为代表了不同的工作频率。 6400: = 6.40 GB/s, (PC3-800 SDRAM, 数据总线8字节宽)8500: = 8.53 GB/s, (PC3-1066 SDRAM, 数据总线8字节宽)10600: = 10.66 GB/s, (PC3-1333 SDRAM, 数据总线8字节宽)12800: = 12.80 GB/s, (PC3-1600 SDRAM, 数据总线8字节宽) m:类型,字面意思,包含有无缓存、寄存器,尺寸等类型 E:无缓冲Unbuffered DIMM (“UDIMM”),带ECC(x72位模块数据总线)F: 全缓冲Fully Buffered DIMM (“FB-DIMM”)M: Micro-DIMMR: Registered DIMM (“RDIMM”)S: Small Outline DIMM(“SO-DIMM”)U: 无缓冲DIMM (“UDIMM”),无ECC(x64位模块数据总线) 一般板卡要用DIMM形式的SDRAM,用的也是SO-DIMM,小型DIMM。 aa: DDR3 SDRAM 最大工作频率时钟的CAS延迟bb: 用于此DIMM的JEDEC SPD修订编码和添加级别cc: 设计使用的参考设计(如适用) A: 使用规范给出的参考设计:raw card ‘A’B: 使用规范给出的参考设计:raw card ‘B’AV: 使用规范给出的参考设计:raw card ‘AV’ZZ: 未使用规范给出的参考设计 d: 所使用的参考设计的修订编号 0: 初始发行版1: 第一次修订2: 第二次修订P: 预发布或工程示例Z: 当字段cc = ZZ时使用所以,我用的这张卡,4GB 1Rx8 PC3L - 12800S - 11 - 11 - B2代表规格为: 4GB DDR3 SO-DIMM,使用1 rank的8bit SDRAM颗粒组成,以DDR3-1600的性能运行,CAS延迟= 11,使用JEDEC DDR3 SPD revision 1.1,参考设计第二次修订版本。 1.2 颗粒标识内存颗粒的丝印可以看到DDR3 SDRAM颗粒的型号为:K4B4G0846E-BYK0 从卡上的三星标志可以知道这个颗粒是三星的。想要初略了解,直接看型号是最直观的。关于三星DDR3命名规范可以在其官网查到:

所以这是 K4B4G0846E-BYK0三星DRAMDDR3 SDRAM4Gb8bit 数据位宽8 bankSSTL电平第6代-FBGA封装商业级温度范围DDR3-1600 (800MHz @ CL=11, tRCD=11, tRP=11)一目了然。 2 204-pin SO-DIMM 规范大概了解后,就要学习怎么使用这个内存条。 DIMM全称Dual-Inline-Memory-Modules,中文名叫双列直插式存储模块,是指奔腾CPU推出后出现的新型内存条,它提供了64位的数据通道。DIMM(Dual Inline Memory Module,双列直插内存模块)与SIMM(single in-line memory module,单边接触内存模组)相当类似,不同的只是DIMM的金手指两端不像SIMM那样是互通的,它们各自独立传输信号,因此可以满足更多数据信号的传送需要。 各种类型的DIMM内存条都有响应的规范设计文件,我使用的这张内存条符合“PC3-6400/PC3-8500/PC3-10600/PC3-12800 DDR3 Unbuffered SO-DIMM Reference Design Specification”,所以需要从这个规范开始学习。 规范提到,参考规范定义了PC3-12800内存模块的电气和机械要求,一个204引脚,800MHz时钟(1600MT/s数据速率),64位宽,无缓冲同步双倍数据数据(Double Data Rate 3,DDR3)DRAM,小型双列直插式存储模块(Small outline Dual In-Line Memory Module, SO-DIMM)DDR3 SDRAM。它还定义了一个较慢的版本,PC3-10600,使用667MHz时钟(1333 MT/s数据速率)DDR3 SDRAM, PC3-8500,使用533MHz时钟(1066 MT/s数据速率)DDR3 SDRAM, PC3-6400,使用400MHz时钟(800 MT/s数据速率)DDR3 SDRAM。这些DDR3 SDRAM so-dimm用于安装在移动个人电脑等系统中作为主内存使用。 2.1 找到本卡在规范中的具体分类

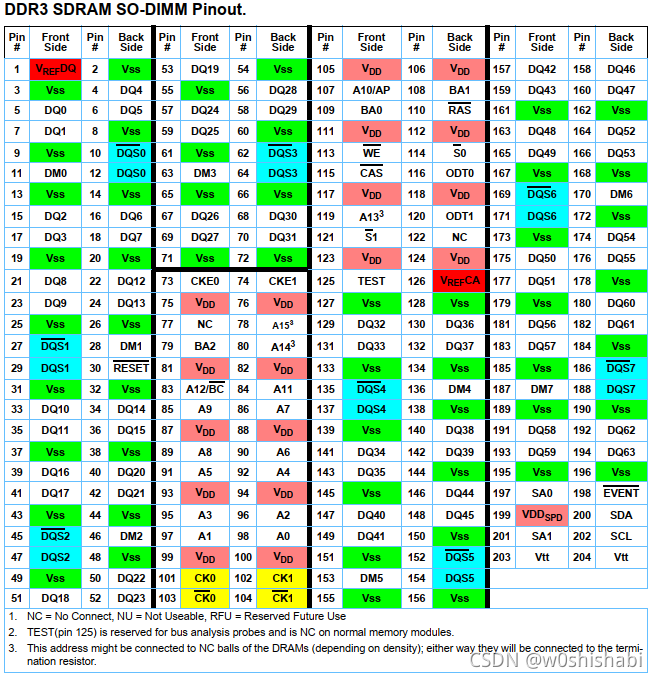

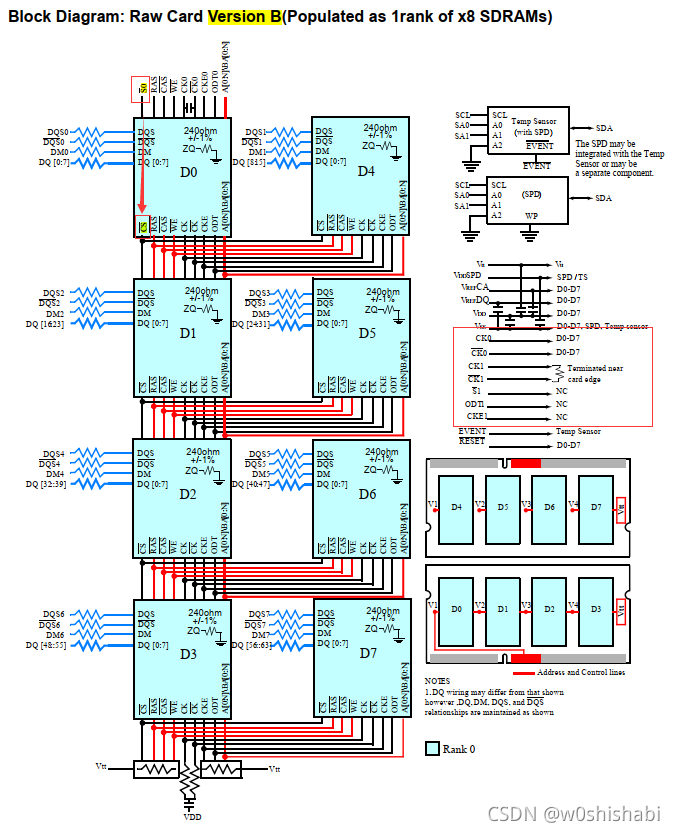

可以看到,我使用的内存条为 8个、x8 数据位宽的颗粒,1 rank 。所以属于B类。 2.2 找到本分类对应的引脚定义与连接首先,可以看到统一的引脚描述,这里只简单列出一下关键引脚,因为我们能看懂原理图各信号的含义与连接即可使用MIG开发。如果要自己写控制器,需要详细学习。 引脚功能描述CK[1:0]差分时钟输入系统时钟输入。所有地址和指令在CK上升沿和~CK下降沿。~CK[1:0]差分时钟输入CKE[1:0]时钟使能用于低功耗或自刷新模式~RASRow Address Stobe行地址选通~CASRow Address Stobe列地址选通~WE写使能~S[1:0]芯片选择低时启用相关的DDR3 SDRAM命令解码器,高时禁用命令解码器。当命令解码器被禁用时,新的命令将被忽略,但之前的操作将继续。rank 0由S0选择;rank 1是由S1选择的A[9:0],A11,A[15:13]地址输入A10/AP地址输入/Autoprecharge自动预充电用于在突发读或写周期结束时调用自动预充电操作。A12/~BC地址输入/Burst chop在READ和WRITE命令期间采样,以确定是否将执行突发BA[2:0]SDRAM Bank AddressDQ[63:0]Data Input/OutputDM[7:0]写模式数据掩码每位控制一个byte,不影响读DQS[7:0]差分数据选通每位控制一个byte,写数据时输入,读数据时输出~DQS[7:0]差分数据选通RESET复位每个引脚在金手指中的位置,了解即可,硬件工程师会设计好:

关键的是要熟悉内存条对应的分类的具体引脚连接。不同类型的引脚功能都一样,但是在比较简单的分类中,一些控制引脚是没用到的。所以这个我们需要知晓一下我们的卡的控制信号的连接。

关注点: 结构为8片颗粒进行位宽扩展。S0信号连接到CS。控制信号高位空载或者直接接了一个负载,未使用,因为只有1 rank。总结一下A、B、C、D类的颗粒排布: 到这里,就可以很好的理解rank的含义了,rank的增加可以理解为在深度上的拓展。有两种方式,一种是平面排布(A),一种是堆叠设计(D)。 3 找到颗粒的关键时序参数其实知道了内存条的类型和容量,颗粒的位宽、容量等参数就已经确定了。 对于我们用的B类,以内存条容量为4GB为例,因为数据位宽固定为64位,所以深度为512M。又因为B类只是位宽拓展,所以颗粒的规格为512Mx8bit,容量为512MB。 MIG的例化还需要设置一些时序参数,其中的值为K4B4G0846E-BYK0的时序参数。关于怎么找这些参数,翻到数据手册Timing Parameters的章节然后搜索就行。 参数描述值tckeCKE最小脉冲宽度8nstfawfour address width,在这个宽度内只能访问不超过四个地址40nstrasActive to Precharge conmmand, Active信号与预充电命令直接的最小间隔37.5nstrcdActive to Read or Write delay, 读或写延迟于Active信号的最小间隔15.0nstrefiAverage periodic refresh interval, 平均周期刷新的最大间隔7.8ustrfcRefresh to Active or Refresh to Refresh, 刷新到active或刷新之间的最小间隔260nstrpPrecharge conmmand period, Precharge命令的处理周期15.0nstrrdActive minimum command period, 不同bank的Active命令间的最小延迟6.0nstrtpRead following a Precharge to the same device, 读命令到Precharge命令间的延迟10.0nstwtrRead following a write to the same device, 写切换到读的最小延迟7.5ns具体了解这些参数的含义需要看“DDR3 SDRAM Standard(JESD79-3F)” 4 参考资料 204-Pin DDR3 SDRAM Unbuffered SO-DIMM Design SpecificationDS_K4B4G0846E_BY_M_Rev1_31-0DDR3 SDRAM Standard(JESD79-3F)可在下面公众号回复21112801获取:

|

【本文地址】