| CPU的基本功能和结构 | 您所在的位置:网站首页 › cpu的功能主要是什么意思 › CPU的基本功能和结构 |

CPU的基本功能和结构

|

CPU的基本功能:

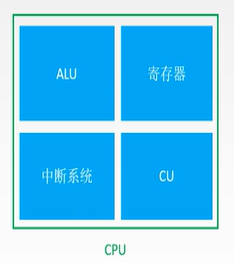

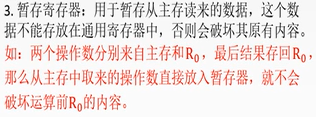

运算器的核心部件就是算术逻辑单元。 算术逻辑单元(Arithmetic&logical Unit) 是中央处理器(CPU)的执行单元,是所有中央处理器的核心组成部分,由"And Gate"(与门) 和"Or Gate"(或门)构成的算术逻辑单元,主要功能是进行二位元的算术运算,如加减乘(不包括整数除法)。基本上,在所有现代CPU体系结构中,二进制都以补码的形式来表示。 在运算中可能会产生一些中间结果,而且有些时候也会把操作数存放在寄存器当中,所以运算器还会有一些寄存器。 而ALU如果想要使用寄存器里面的数据的话,就需要在寄存器和ALU之间连通线路了,下面就介绍两种连线方式: ① 专用数据连通方式: ② CPU内部单总线方式: 在CPU内部设置一条叫做CPU内部总线的公共通路,让ALU和寄存器都与总线连接,任意两个部件的传输都是经过这条总线来实现的,假如要把R0的数据放到R1当中,就需要把R0out打开,把R0的数据放到总线上,再把R1in的开关打开,把数据放到R1里面;如果同一时刻,R2和R3也想要进行数据的传输,就需要等待前面过程的完成才能请求总线的服务。 现在,寄存器的数据可以通过总线进行传输,同时这些数据也有可能会作为ALU的输入,因此可以把ALU的输入端与总线进行连接。 可以在其中一端的线路上设置一个暂存寄存器: 注: 暂存寄存器还有一个功能: 假如经过ALU的运算后加法的结果要存回的是寄存器R0,这是就需要把ALU的输出端与总线进行连接,那么ALU的输出也是会通过总线传输,不过现在问题发生了 ,只有ALU的两个输入端等到输入的信号稳定后,这次的运算才有可能得到正确的结果,但是因为其中一个操作数是来自R0,而且在R0给的输入信号还没稳定之前ALU就已经产生一个输出信号送到总线,这样就会与R0送到总线的电信号产生冲突,这就会导致运算的错误,那这个问题又该如何解决? 只需要再设置一个暂存寄存器和三态门即可,这样的话就可以等待R0输入到ALU的信号稳定之后,ALU会先把运算结果放到暂存寄存器当中,等ALU的输出结果稳定之后再连通三态门,把运算结果传输到总线上,连通R0的输入端,就可以把加法运算的正确结果输入回R0。 CPU内部单总线方式的特点:

|

【本文地址】

| 今日新闻 |

| 推荐新闻 |

| 专题文章 |

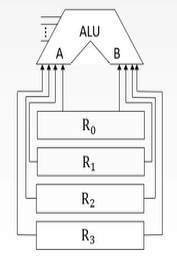

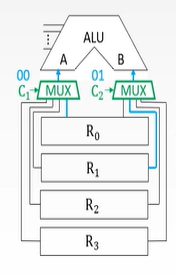

因为寄存器可能会给ALU中两个输入端任意一端发送数据,所以每个寄存器都需要同时与A和B同时连线,图中用一条线来表示,实际上连线数与寄存器中的位数一致。

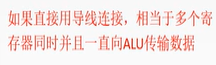

因为寄存器可能会给ALU中两个输入端任意一端发送数据,所以每个寄存器都需要同时与A和B同时连线,图中用一条线来表示,实际上连线数与寄存器中的位数一致。  连接完成,但是此时的线路会存在一个问题:

连接完成,但是此时的线路会存在一个问题:  但是该如何解决这种问题呢?

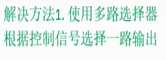

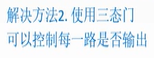

但是该如何解决这种问题呢?

控制信号为1时线路连通,可以输出数据,为0时反之。

控制信号为1时线路连通,可以输出数据,为0时反之。  专用数据连通方式的特点:

专用数据连通方式的特点:

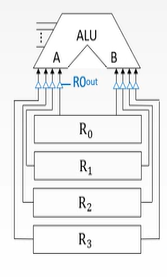

但是采用现在的连线方式会导致总线的冲突,假如R0和R1要进行加法操作,R0和R1的数据同时传输到总线上,传输到ALU时就无法判断两个输入端分别是什么数据,那么如何解决这个问题呢?

但是采用现在的连线方式会导致总线的冲突,假如R0和R1要进行加法操作,R0和R1的数据同时传输到总线上,传输到ALU时就无法判断两个输入端分别是什么数据,那么如何解决这个问题呢? 设置了暂存寄存器后,这样的话就可以先把一个寄存器R0内的数据传输到总线上,通过总线R0的数据会被存放到暂存寄存器当中,然后让R0输出的三态门有效信号失效,再导通R1的输出信号,让R1的数据输出到另外一端,这样的话就可以保证内部单总线的方式可以正常地工作。

设置了暂存寄存器后,这样的话就可以先把一个寄存器R0内的数据传输到总线上,通过总线R0的数据会被存放到暂存寄存器当中,然后让R0输出的三态门有效信号失效,再导通R1的输出信号,让R1的数据输出到另外一端,这样的话就可以保证内部单总线的方式可以正常地工作。 那么接下来再考虑ALU计算之后的结果该如何存放?

那么接下来再考虑ALU计算之后的结果该如何存放?

运算器小结:

运算器小结: