| Cadence SPB 22.1 | 您所在的位置:网站首页 › allegro怎么关掉vg的drc › Cadence SPB 22.1 |

Cadence SPB 22.1

|

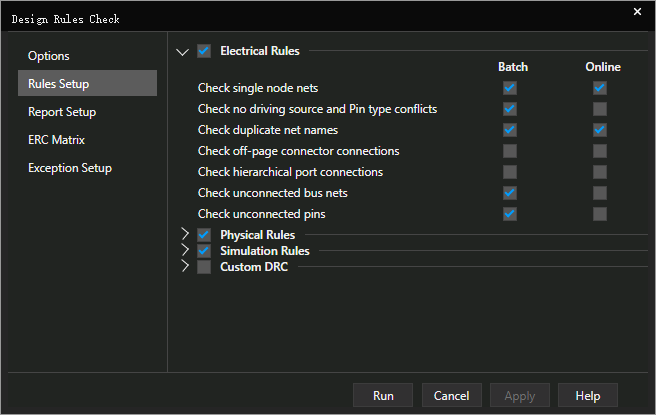

一、原理图编译的规则设置 1、online DRC ①、 on:开启在线DRC ②、off :关闭在线DRC 2、DRC Action ①、Run On Design: DRC检查整个原理图 ②、Run On Selection: DRC检查选择的部分电路 ③、Delete DRC Markers: 删除DRC标记 ④、Delete DRC Markers on Selection:删除所选的 DRC 标记 3、Use Properties(Mode) ①、Occurrences:选择所有事件进行检查 ②、Instances(Preferred):使用当前实体(建议)。所谓实体是指放在绘图页内的元器件符号,而事件指的是在绘图页内同一实体出现多次的实体电路。 ③、Check Design Rules:对当前的设计文件进行 DRC 检测 ④、Delete Existing DRC Marker:删除 DRC 检测标志 Report 4、Warning ①、Create DRC Markers:进行 DRC 检测,若发现错误,则生成警告标志 ②、Do Not Create DRC Markers:进行 DRC 检测,若发现错误,则不生成警告标志。

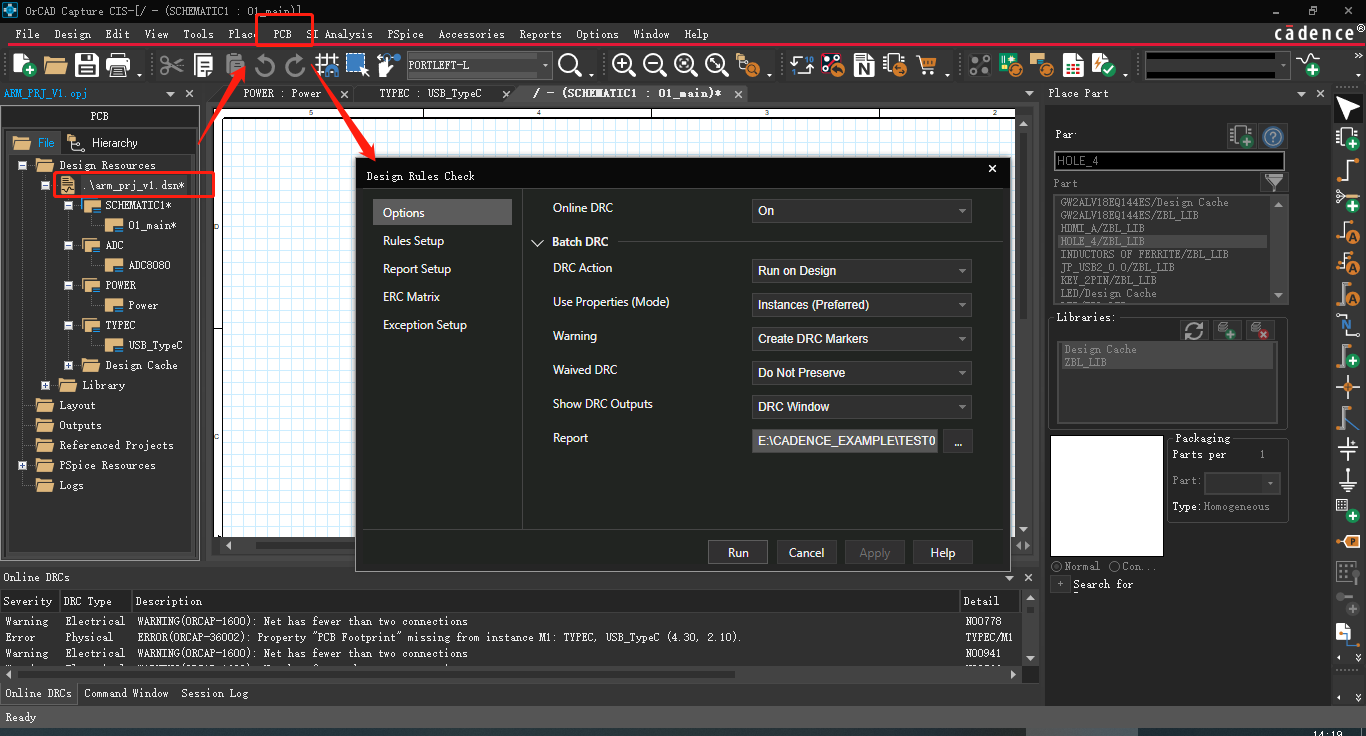

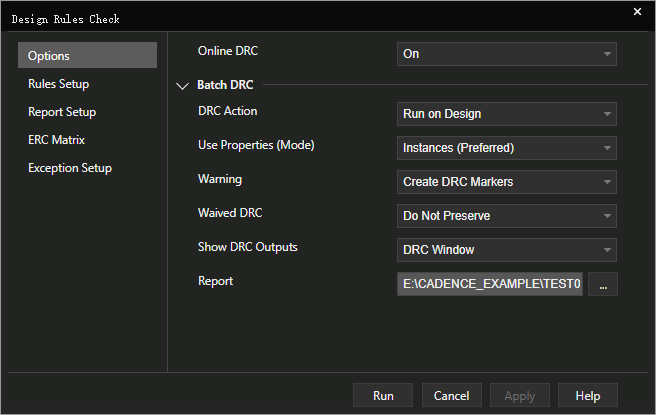

二、 原理图编译 1、选择原理图的根目录(.DSN),执行菜单命令“PCB”→“Design Rules Check”,进行设计规则的检查 2、弹窗的DRC检查界面中,有4项参数可以进行设置, ①、Options:为检查的参数设置,与上一节的规则设置相关。 ②、Rules Setup: 其中Electrical Rules为电气规则检查参数设置。 ③、Rules Setup:其中Physical Rules为物理规则检查参数设置,还有模拟仿真检查参数设置 ④、DRC Matrix :为 DRC 矩阵设置是否报 DRC(一般保持默认即可)。 3、确认规则设置OK后,点击Run对该原理图进行规则检查。之后根据报告的报错信息进行修改原理图。

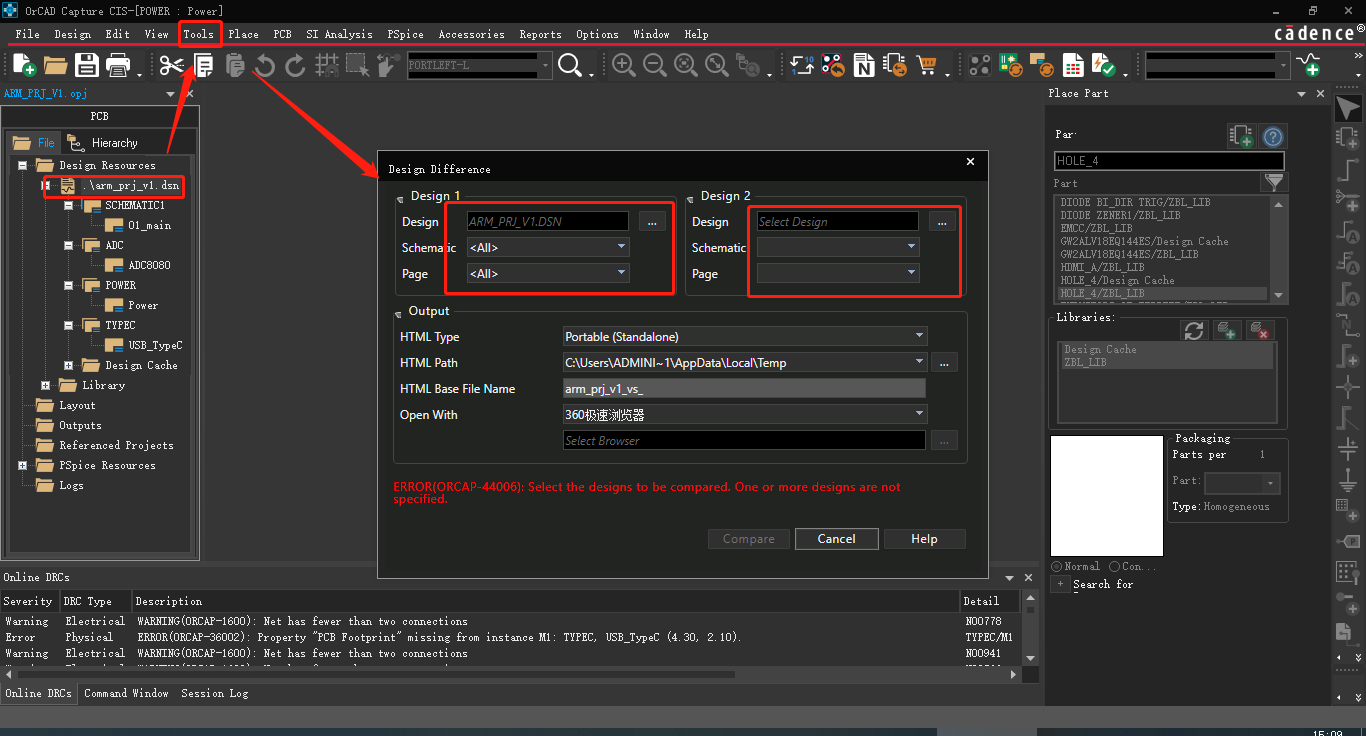

三、原理图差异对比(与之前的Accessoriesr入口不同) 1、打开需要对比的任一原理图,选择原理图的根目录(.DSN),执行菜单栏命令“Tools”→ “Compare Designs”进行原理图对比。 2、弹出对话框,选择对比两份原理图选项,点击“Launch”按键后,执行原理图对比 3、选择需要对比的两份原理图,进行对比即可。单击下面的“Compare”按钮进行对比。

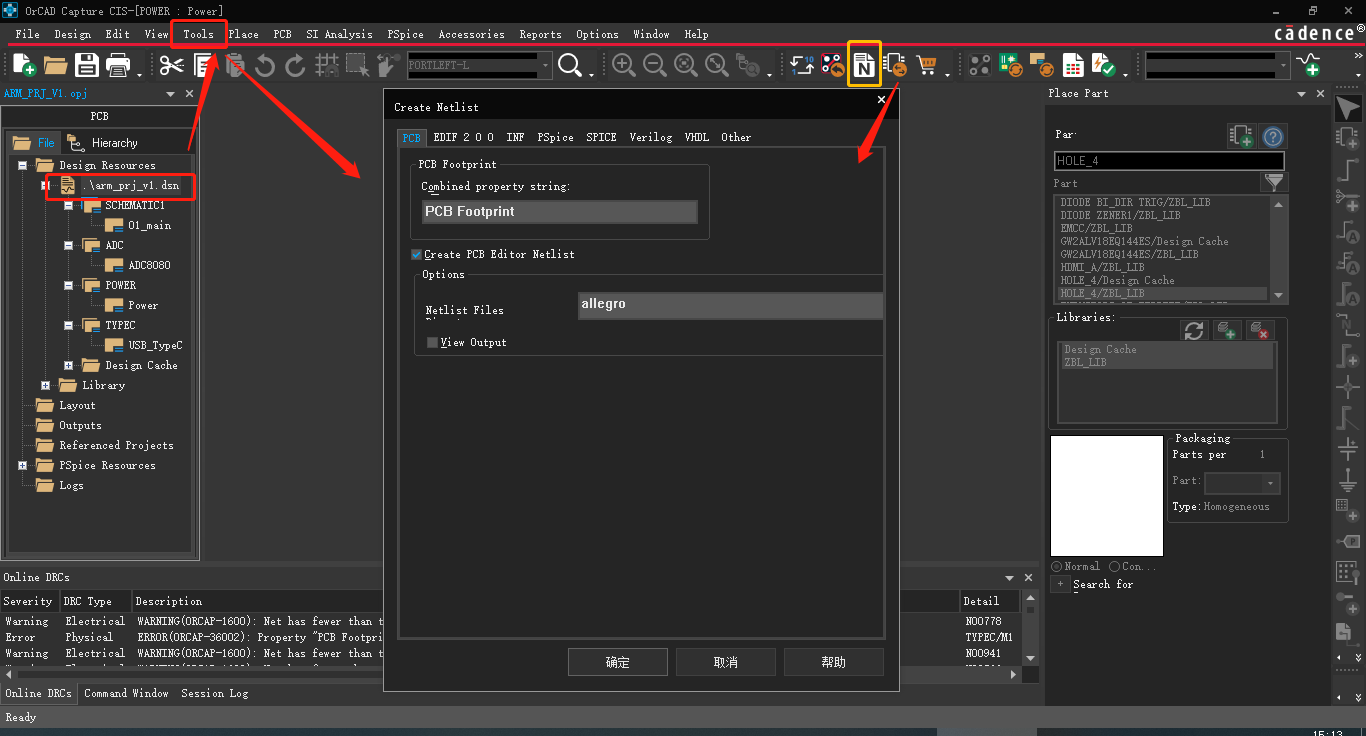

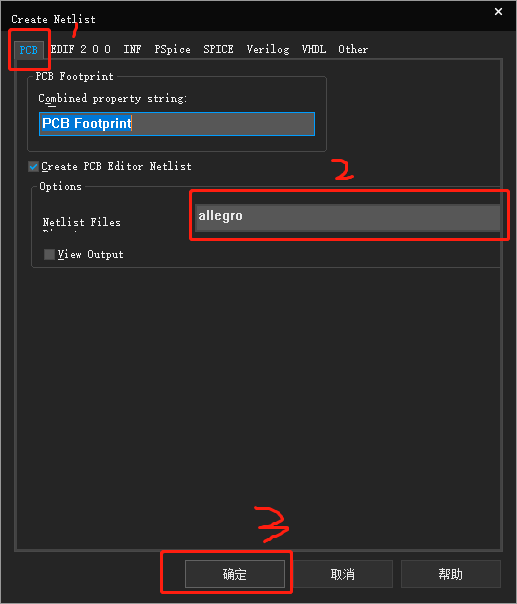

四、第一方网表输出 1、 选择原理图的根目录(.DSN),执行菜单栏命令“Tools”→“Create Netlist”,或者单击菜单栏上的图标,调出产生网表的界面。 2、选择“PCB”选项栏,产生 Allegro 的第一方网表。 3、输出 Allegro 第一方网表需要注意下面几个地方 ①、需要勾选“Creat PCB Editor Netlist”,才会生成网表。 ②、下面的“Netlist Files”是输出网表的存储路径,不进行更改的话,表示在当前原理图目录下会自动产生“allegro”的文件夹,里面就是输出的网表。 ③、单击右侧的“Setup”按钮,如图 下图 所示,如果勾选“Ignore Electrical Constraints”选项,则忽略原理图中所添加的规则。

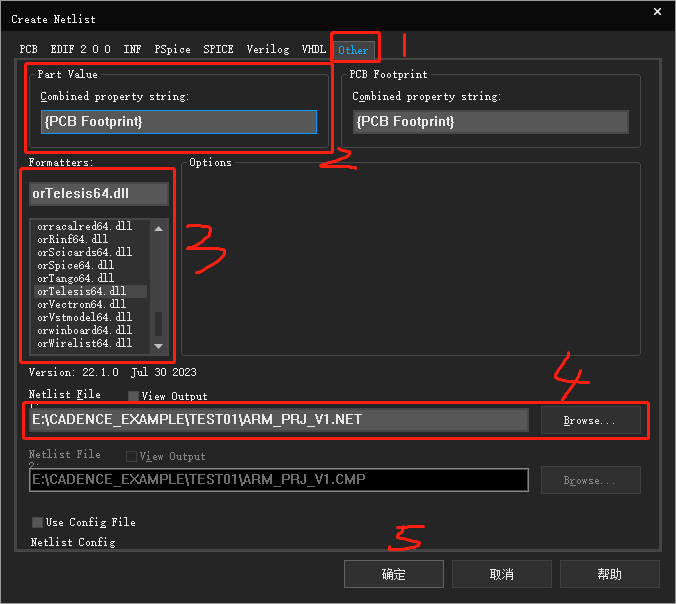

五、第三方网表输出 OrCAD 产生 Cadence Allegro 的网表的操作步骤如下: 1、 选择原理图的根目录(.DSN),执行菜单栏命令“Tools”→“Create Netlist”,或者单击菜单栏上的图标,调出产生网表的界面。 2、选择“Other”选项栏,产生 Other的第三方网表。在“Formatters” 栏中选择“orTelesis64.dll” 选项, 在“Part Value” 栏中需要用“PCB Footprint”来代替,不然会产生错误。 3、按照步骤2中所述的设置好参数后,在下方的路径中选择网表存储的路径,默认路径是当前原理图所处的路径。 单击“确定”按钮, 即可输出第三方的网表文件, 后缀是.NET的文件就是网表文件。

备注说明 Allegro 的第一网表与第三网表的差异及使用 1、与 Allegro 能实现交互式操作的是第一方网表,而第三方网表不能实现交互式操作 2、第三方网表不能将器件的 Value 属性导入 PCB 中,输出时以封装属性来代替 Value 属性,而第一方网表是可以的。 3、网表导入 PCB 时,第三方网表需要事先指定 PCB 封装库文件,并产生 device 文件,这样才能将网表导入 PCB 中,而第一方网表则可以直接导入。 4、严谨规范的设计建议使用第一方网表,第三方网表相对限制条件会宽松些。

|

【本文地址】