| 利用 vivado实现 运算器的设计 | 您所在的位置:网站首页 › Verilog加减法运算 › 利用 vivado实现 运算器的设计 |

利用 vivado实现 运算器的设计

|

运算器的设计

一、实验目的和要求二、实验内容和原理三、主要仪器设备四、操作方法与实验步骤8 位运算器的设计用 Block Design 设计 8 位运算器

五、实验数据记录和处理七、讨论、心得

一、实验目的和要求

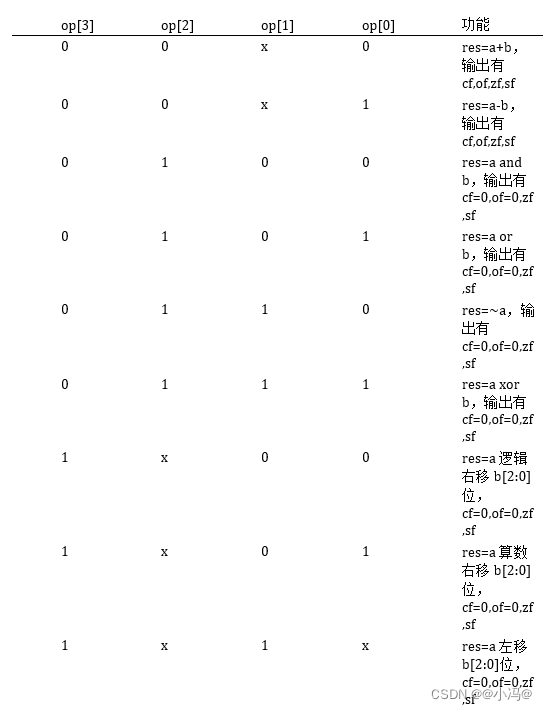

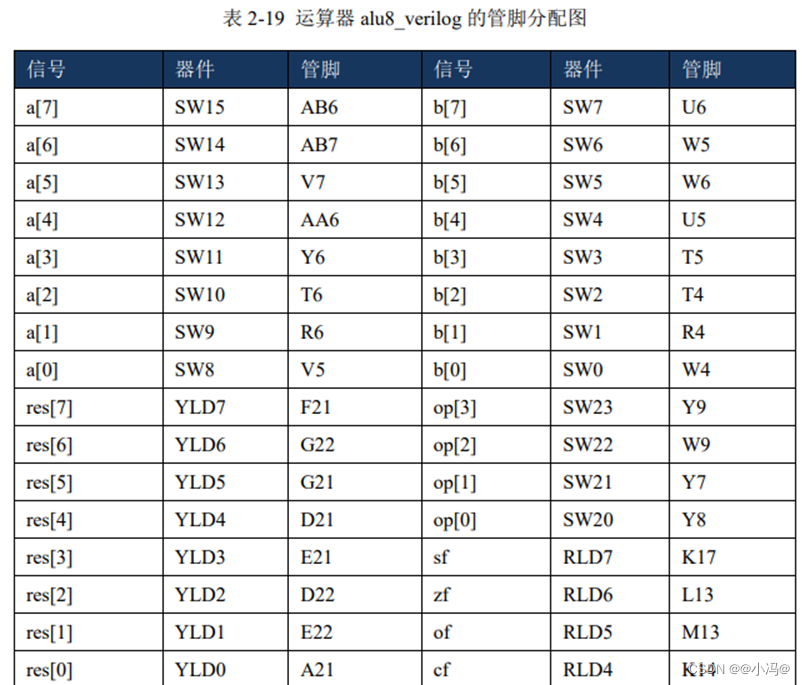

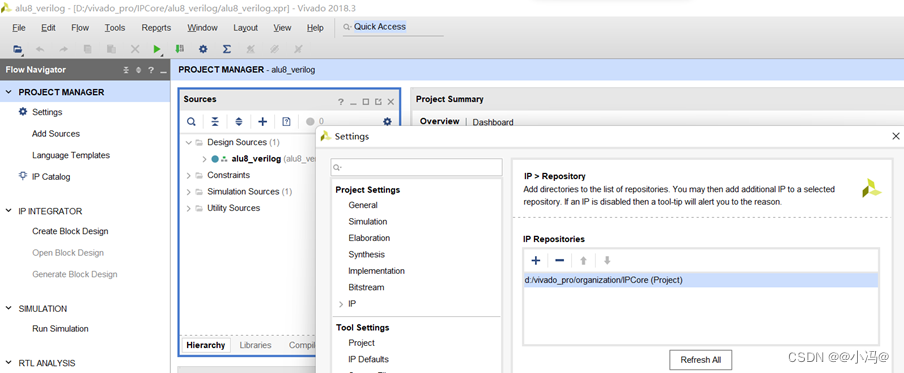

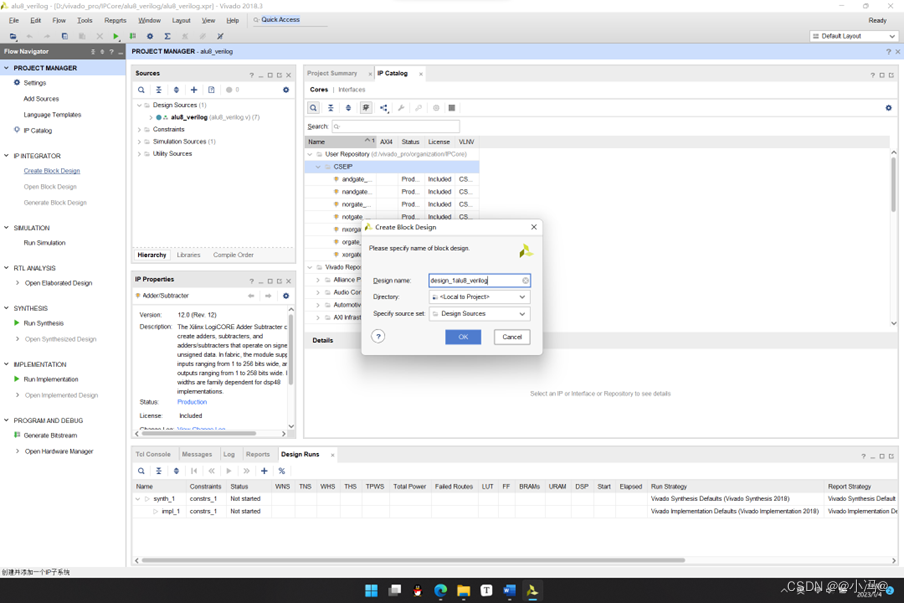

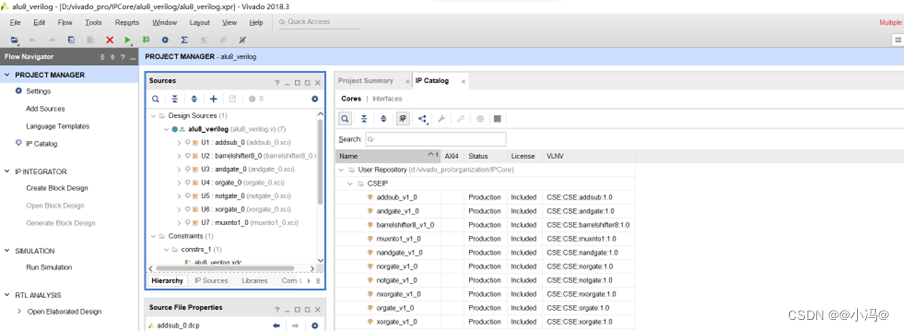

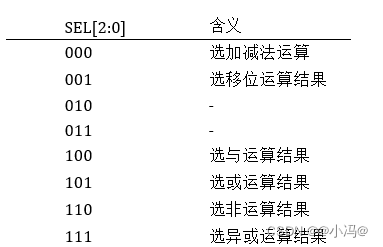

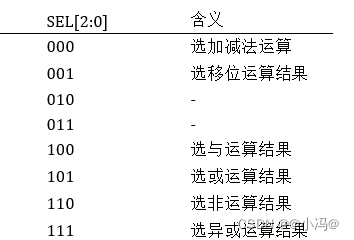

1.通过实验,将前面设计的 IP 核进行综合应用,初步理解指令格式,学会设计运算器的控制逻辑。 2.通过实验,进一步熟悉 Block Design 的设计方法,设计一个能进行算术运算(加、减法)、 逻辑运算(与、或、非、异或)和移位运算(逻辑左移、算术左移、逻辑右移、算术右移) 的 8 位运算器。 二、实验内容和原理1.利用前面几章设计好的可变数据位数的加减法器 IP 核以及可配置输入端数目和数据位宽的与、或、非、异或门、多路选择器 IP 核以及 8 位桶形移位器 IP 核作为基本元件,利用 Vivado 的 Block Design 或者利用 Verilog 的结构化描述方法与数据流描述方法完成一个 8 位的运算器 alu8_verilog,其功能如下表所示。其中 op[3:0]是操作码,输入的 8 位操作数分 别是 a[7:0]和 b[7:0],运算结果是 res[7:0],另外输出还有进位标志 cf,有符号数溢出标志 of, 结果为 0 标志 zf 以及有符号数符号标志 sf。 2.利用前面几章设计好的可变数据位数的加减法器 IP 核、与、或、非、异或门 IP 核、8 位桶形移位器 IP 核以及 8 选 1 多路选择器 IP 核作为基本元件,利用 Vivado 的 Block Design 完成一个 8 位的运算器 alu8_bk。 将你的设计综合、实现、并下载到 Minisys 实验板上,信号与管脚的对应关系是: a[7:0]-sw15-sw8,b[7:0]-sw7-sw0,op[3:0]-sw23sw20,res[7:0]-YLD7YLD0,cf-RLD4, of-RLD5,zf-RLD6,sf-RLD7。各信号对应的板上器件及其管脚如表 2-19 所示。 个人电脑:Huawei Matebook 14 Windows 11 家庭中文版 类型:64位 处理器:Intel® Core™ i5-10210U CPU @ 1.60GHz 2.11 GHz 内存:16GB 四、操作方法与实验步骤 8 位运算器的设计 将以前做过的IP核调入到项目的IP核库中 图3-1 创建项目lu8_verilog 图3-1 创建项目lu8_verilog  图3-2 导入IP核通过 IP Catalog 将需要使用的 IP 核以 8 位数据宽度,两输入形式添加到 project 中。 图3-2 导入IP核通过 IP Catalog 将需要使用的 IP 核以 8 位数据宽度,两输入形式添加到 project 中。 图3-3 添加IP核到项目中设计好 8 选 1 的选择端的逻辑电路。8 选 1 的选择端只有 3 位,因此,要将 4 位的 op 转换成 3 位的选择端 SEL[2:0]。下表中定义了 SEL[2:0]各种取值的含义。 图3-3 添加IP核到项目中设计好 8 选 1 的选择端的逻辑电路。8 选 1 的选择端只有 3 位,因此,要将 4 位的 op 转换成 3 位的选择端 SEL[2:0]。下表中定义了 SEL[2:0]各种取值的含义。 设计源文件alu8_verilog.v,并向文件中写入如下内容:

`timescale 1ns / 1ps

module alu8_verilog(

input [7:0] a, // 操作数1

input [7:0] b, // 操作数2

input [3:0] op, // 操作码

output [7:0] res, // 运算结果

output cf, // 进位标志

output ovf, // 有符号数溢出标志

output zf, // 结果是否为0

output sf // 符号标志

);

wire [7:0] res0;

wire [7:0] res1;

wire [7:0] res2;

wire [7:0] res3;

wire [7:0] res4;

wire [7:0] res5;

wire [7:0] res6;

wire [7:0] res7;

// res0 是加减法的结果 加法00x0 减法00x1

// 所以加减法的标志是00xx sub取的是op最右一位

// cf和ovf可以完全由addsub决定,但是sf和zf不能

wire helpSf1;

wire helpSf2;

wire helpZf1;

wire helpZf2;

wire helpCf;

wire helpOvf;

addsub_0 uAddsub(.a(a), .b(b), .sub(op[0]), .sum(res0), .cf(helpCf), .ovf(helpOvf), .sf(helpSf1), .zf(helpZf1));

// res1 是移位的结果 逻辑右移1x00 算术右移1x01 左移1x1x

// 所以左移是1x1x 右移是1x0x 根据op最后一位决定是逻辑右移还是算数右移

// 所以移位的标志是1xxx

// 移位标志:1x左移 00逻辑右移 01算数右移

wire [1:0] shifterFlag = op[1] ? 2'b11 : // 左移

op[0] ? 2'b01 : // 算数右移

2'b00; // 逻辑右移

barrelshifter8_0 uShifter(.d(a), .s(b[2:0]), .t(shifterFlag), .q(res1));

// res2和res3正常情况下都不会选到,所以都设置为0

assign res2 = 8'b0;

assign res3 = 8'b0;

// res4 是a和b进行&的操作

andgate_0 uAndgate(.a(a), .b(b), .q(res4));

// res5 是a和b进行|的操作

orgate_0 uOrgate(.a(a), .b(b), .q(res5));

// res6 是a进行取反的操作

notgate_0 uNotgate(.a(a), .c(res6));

// res7 是a和b进行异或的操作

xorgate_0 uXorgate(.a(a), .b(b), .q(res7));

wire [2:0] selectFlag;

assign selectFlag = (op[3:2] == 2'b00) ? 3'b000 :

(op[3] == 1'b1) ? 3'b001 :

(op == 4'b0100) ? 3'b100 :

(op == 4'b0101) ? 3'b101 :

(op == 4'b0110) ? 3'b110 :

3'b111;

muxnto1_0 uMux(

.a0(res0),

.a1(res1),

.a2(res2),

.a3(res3),

.a4(res4),

.a5(res5),

.a6(res6),

.a7(res7),

.s(selectFlag),

.q(res)

);

assign helpSf2 = res[7];

assign helpZf2 = (res == 8'b0);

assign sf = (selectFlag == 3'b000) ? helpSf1 : helpSf2;

assign zf = (selectFlag == 3'b000) ? helpZf1 : helpZf2;

assign cf = (selectFlag == 3'b000) ? helpCf : 1'b0;

assign ovf = (selectFlag == 3'b000) ? helpOvf : 1'b0;

endmodule

设计仿真文件alu8_verilog_sim.v,并向其中写入如下内容:

`timescale 1ns / 1ps

module alu8_verilog_sim( );

// input

reg [7:0] a = 8'h16;

reg [7:0] b = 8'h12;

reg [3:0] op = 4'b0000; // 加法

//output

wire [7:0] res;

wire cf;

wire ovf;

wire sf;

wire zf;

// initial

alu8_verilog U (.a(a),.b(b),.op(op),.res(res),.cf(cf),

.ovf(ovf),.sf(sf),.zf(zf));

initial begin

#200 op = 4'b0001; // 减法

#200 begin a = 8'h7f; b = 8'h2; op = 4'b0000; end

#200 begin a = 8'hff; b = 8'h2; op = 4'b0000; end

#200 begin a = 8'h16; b = 8'h17; op = 4'b0001; end

#200 begin a = 8'hf0; b = 8'h0f; op = 4'b0100; end // 与

#200 begin a = 8'hf0; b = 8'h0f; op = 4'b0101; end // 或

#200 begin a = 8'hf0; b = 8'h0f; op = 4'b0110; end // 非

#200 begin a = 8'hff; b = 8'hff; op = 4'b0111; end // 异或

#200 begin a = 8'hff; b = 8'h03; op = 4'b1000; end//逻辑右移

#200 begin a = 8'hff; b = 8'h03; op = 4'b1001; end//算数右移

#200 begin a = 8'hff; b = 8'h03; op = 4'b1010; end // 左移

#200 ;

end

endmodule

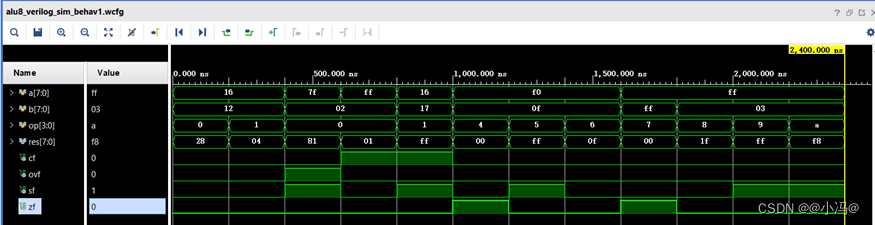

仿真结束之后,得到如下波形: 设计源文件alu8_verilog.v,并向文件中写入如下内容:

`timescale 1ns / 1ps

module alu8_verilog(

input [7:0] a, // 操作数1

input [7:0] b, // 操作数2

input [3:0] op, // 操作码

output [7:0] res, // 运算结果

output cf, // 进位标志

output ovf, // 有符号数溢出标志

output zf, // 结果是否为0

output sf // 符号标志

);

wire [7:0] res0;

wire [7:0] res1;

wire [7:0] res2;

wire [7:0] res3;

wire [7:0] res4;

wire [7:0] res5;

wire [7:0] res6;

wire [7:0] res7;

// res0 是加减法的结果 加法00x0 减法00x1

// 所以加减法的标志是00xx sub取的是op最右一位

// cf和ovf可以完全由addsub决定,但是sf和zf不能

wire helpSf1;

wire helpSf2;

wire helpZf1;

wire helpZf2;

wire helpCf;

wire helpOvf;

addsub_0 uAddsub(.a(a), .b(b), .sub(op[0]), .sum(res0), .cf(helpCf), .ovf(helpOvf), .sf(helpSf1), .zf(helpZf1));

// res1 是移位的结果 逻辑右移1x00 算术右移1x01 左移1x1x

// 所以左移是1x1x 右移是1x0x 根据op最后一位决定是逻辑右移还是算数右移

// 所以移位的标志是1xxx

// 移位标志:1x左移 00逻辑右移 01算数右移

wire [1:0] shifterFlag = op[1] ? 2'b11 : // 左移

op[0] ? 2'b01 : // 算数右移

2'b00; // 逻辑右移

barrelshifter8_0 uShifter(.d(a), .s(b[2:0]), .t(shifterFlag), .q(res1));

// res2和res3正常情况下都不会选到,所以都设置为0

assign res2 = 8'b0;

assign res3 = 8'b0;

// res4 是a和b进行&的操作

andgate_0 uAndgate(.a(a), .b(b), .q(res4));

// res5 是a和b进行|的操作

orgate_0 uOrgate(.a(a), .b(b), .q(res5));

// res6 是a进行取反的操作

notgate_0 uNotgate(.a(a), .c(res6));

// res7 是a和b进行异或的操作

xorgate_0 uXorgate(.a(a), .b(b), .q(res7));

wire [2:0] selectFlag;

assign selectFlag = (op[3:2] == 2'b00) ? 3'b000 :

(op[3] == 1'b1) ? 3'b001 :

(op == 4'b0100) ? 3'b100 :

(op == 4'b0101) ? 3'b101 :

(op == 4'b0110) ? 3'b110 :

3'b111;

muxnto1_0 uMux(

.a0(res0),

.a1(res1),

.a2(res2),

.a3(res3),

.a4(res4),

.a5(res5),

.a6(res6),

.a7(res7),

.s(selectFlag),

.q(res)

);

assign helpSf2 = res[7];

assign helpZf2 = (res == 8'b0);

assign sf = (selectFlag == 3'b000) ? helpSf1 : helpSf2;

assign zf = (selectFlag == 3'b000) ? helpZf1 : helpZf2;

assign cf = (selectFlag == 3'b000) ? helpCf : 1'b0;

assign ovf = (selectFlag == 3'b000) ? helpOvf : 1'b0;

endmodule

设计仿真文件alu8_verilog_sim.v,并向其中写入如下内容:

`timescale 1ns / 1ps

module alu8_verilog_sim( );

// input

reg [7:0] a = 8'h16;

reg [7:0] b = 8'h12;

reg [3:0] op = 4'b0000; // 加法

//output

wire [7:0] res;

wire cf;

wire ovf;

wire sf;

wire zf;

// initial

alu8_verilog U (.a(a),.b(b),.op(op),.res(res),.cf(cf),

.ovf(ovf),.sf(sf),.zf(zf));

initial begin

#200 op = 4'b0001; // 减法

#200 begin a = 8'h7f; b = 8'h2; op = 4'b0000; end

#200 begin a = 8'hff; b = 8'h2; op = 4'b0000; end

#200 begin a = 8'h16; b = 8'h17; op = 4'b0001; end

#200 begin a = 8'hf0; b = 8'h0f; op = 4'b0100; end // 与

#200 begin a = 8'hf0; b = 8'h0f; op = 4'b0101; end // 或

#200 begin a = 8'hf0; b = 8'h0f; op = 4'b0110; end // 非

#200 begin a = 8'hff; b = 8'hff; op = 4'b0111; end // 异或

#200 begin a = 8'hff; b = 8'h03; op = 4'b1000; end//逻辑右移

#200 begin a = 8'hff; b = 8'h03; op = 4'b1001; end//算数右移

#200 begin a = 8'hff; b = 8'h03; op = 4'b1010; end // 左移

#200 ;

end

endmodule

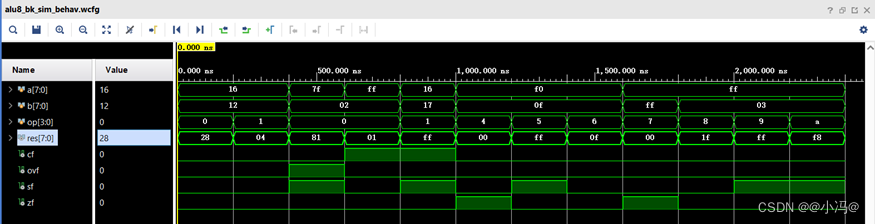

仿真结束之后,得到如下波形:  图3-4 8位运算器仿真波形

用 Block Design 设计 8 位运算器

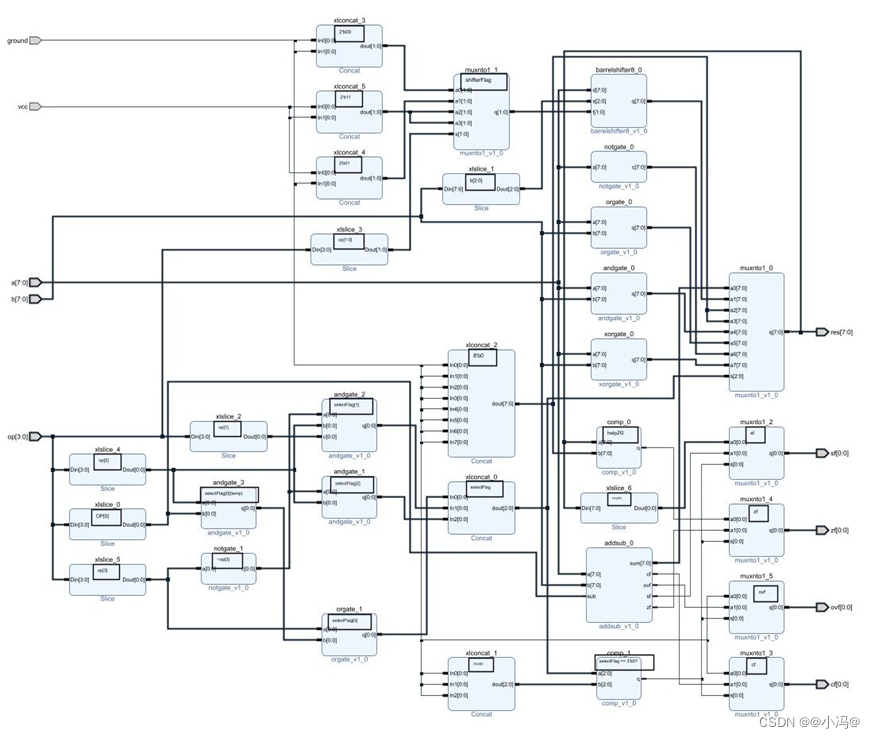

将以前做过的IP核调入到项目的IP核库中。设计好 8 选 1 的选择端的逻辑电路。根据下表中的设计好逻辑表达式。并调用基本门电路的 IP 核,实现这些逻辑表达式。 图3-4 8位运算器仿真波形

用 Block Design 设计 8 位运算器

将以前做过的IP核调入到项目的IP核库中。设计好 8 选 1 的选择端的逻辑电路。根据下表中的设计好逻辑表达式。并调用基本门电路的 IP 核,实现这些逻辑表达式。 用线将各个IP模块的信号连接起来 用线将各个IP模块的信号连接起来  图3-5 IP模块线路图 4. 创建仿真文件alu8_bk_sim.v并填入如下内容:

`timescale 1ns / 1ps

module alu8_bk_sim( );

// input

reg [7:0] a = 8'h16;

reg [7:0] b = 8'h12;

reg [3:0] op = 4'b0000; // 加法

//output

wire [7:0] res;

wire cf;

wire ovf;

wire sf;

wire zf;

// initial

alu8_bk U (.a(a),.b(b),.op(op),.res(res),.cf(cf),

.ovf(ovf),.sf(sf),.zf(zf));

initial begin

#200 op = 4'b0001; // 减法

#200 begin a = 8'h7f; b = 8'h2; op = 4'b0000; end

#200 begin a = 8'hff; b = 8'h2; op = 4'b0000; end

#200 begin a = 8'h16; b = 8'h17; op = 4'b0001; end

#200 begin a = 8'hf0; b = 8'h0f; op = 4'b0100; end // 与

#200 begin a = 8'hf0; b = 8'h0f; op = 4'b0101; end // 或

#200 begin a = 8'hf0; b = 8'h0f; op = 4'b0110; end // 非

#200 begin a = 8'hff; b = 8'hff; op = 4'b0111; end // 异或

#200 begin a = 8'hff; b = 8'h03; op = 4'b1000; end//逻辑右移

#200 begin a = 8'hff; b = 8'h03; op = 4'b1001; end//算数右移

#200 begin a = 8'hff; b = 8'h03; op = 4'b1010; end // 左移

#200 ;

end

endmodule

仿真结束后得到如下图像: 图3-5 IP模块线路图 4. 创建仿真文件alu8_bk_sim.v并填入如下内容:

`timescale 1ns / 1ps

module alu8_bk_sim( );

// input

reg [7:0] a = 8'h16;

reg [7:0] b = 8'h12;

reg [3:0] op = 4'b0000; // 加法

//output

wire [7:0] res;

wire cf;

wire ovf;

wire sf;

wire zf;

// initial

alu8_bk U (.a(a),.b(b),.op(op),.res(res),.cf(cf),

.ovf(ovf),.sf(sf),.zf(zf));

initial begin

#200 op = 4'b0001; // 减法

#200 begin a = 8'h7f; b = 8'h2; op = 4'b0000; end

#200 begin a = 8'hff; b = 8'h2; op = 4'b0000; end

#200 begin a = 8'h16; b = 8'h17; op = 4'b0001; end

#200 begin a = 8'hf0; b = 8'h0f; op = 4'b0100; end // 与

#200 begin a = 8'hf0; b = 8'h0f; op = 4'b0101; end // 或

#200 begin a = 8'hf0; b = 8'h0f; op = 4'b0110; end // 非

#200 begin a = 8'hff; b = 8'hff; op = 4'b0111; end // 异或

#200 begin a = 8'hff; b = 8'h03; op = 4'b1000; end//逻辑右移

#200 begin a = 8'hff; b = 8'h03; op = 4'b1001; end//算数右移

#200 begin a = 8'hff; b = 8'h03; op = 4'b1010; end // 左移

#200 ;

end

endmodule

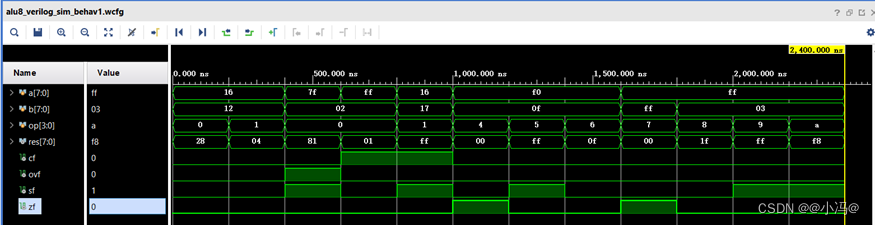

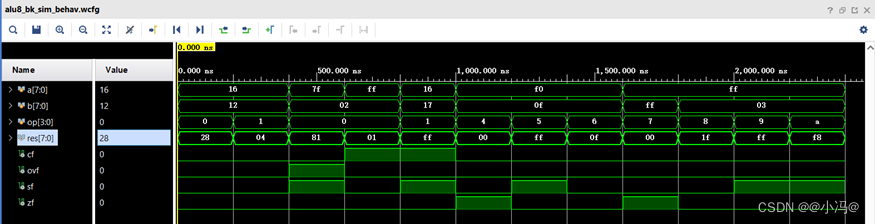

仿真结束后得到如下图像:  图3-6 用 Block Design 设计的 8 位运算器仿真波形

五、实验数据记录和处理

8 位运算器设计中的仿真文件alu8_verilog_sim.v:

`timescale 1ns / 1ps

module alu8_verilog_sim( );

// input

reg [7:0] a = 8'h16;

reg [7:0] b = 8'h12;

reg [3:0] op = 4'b0000; // 加法

//output

wire [7:0] res;

wire cf;

wire ovf;

wire sf;

wire zf;

// initial

alu8_verilog U (.a(a),.b(b),.op(op),.res(res),.cf(cf),

.ovf(ovf),.sf(sf),.zf(zf));

initial begin

#200 op = 4'b0001; // 减法

#200 begin a = 8'h7f; b = 8'h2; op = 4'b0000; end

#200 begin a = 8'hff; b = 8'h2; op = 4'b0000; end

#200 begin a = 8'h16; b = 8'h17; op = 4'b0001; end

#200 begin a = 8'hf0; b = 8'h0f; op = 4'b0100; end // 与

#200 begin a = 8'hf0; b = 8'h0f; op = 4'b0101; end // 或

#200 begin a = 8'hf0; b = 8'h0f; op = 4'b0110; end // 非

#200 begin a = 8'hff; b = 8'hff; op = 4'b0111; end // 异或

#200 begin a = 8'hff; b = 8'h03; op = 4'b1000; end//逻辑右移

#200 begin a = 8'hff; b = 8'h03; op = 4'b1001; end//算数右移

#200 begin a = 8'hff; b = 8'h03; op = 4'b1010; end // 左移

#200 ;

end

endmodule

用 Block Design 设计的 8 位运算器中使用的仿真文件alu8_bk_sim.v:

`timescale 1ns / 1ps

module alu8_bk_sim( );

// input

reg [7:0] a = 8'h16;

reg [7:0] b = 8'h12;

reg [3:0] op = 4'b0000; // 加法

//output

wire [7:0] res;

wire cf;

wire ovf;

wire sf;

wire zf;

// initial

alu8_bk U (.a(a),.b(b),.op(op),.res(res),.cf(cf),

.ovf(ovf),.sf(sf),.zf(zf));

initial begin

#200 op = 4'b0001; // 减法

#200 begin a = 8'h7f; b = 8'h2; op = 4'b0000; end

#200 begin a = 8'hff; b = 8'h2; op = 4'b0000; end

#200 begin a = 8'h16; b = 8'h17; op = 4'b0001; end

#200 begin a = 8'hf0; b = 8'h0f; op = 4'b0100; end // 与

#200 begin a = 8'hf0; b = 8'h0f; op = 4'b0101; end // 或

#200 begin a = 8'hf0; b = 8'h0f; op = 4'b0110; end // 非

#200 begin a = 8'hff; b = 8'hff; op = 4'b0111; end // 异或

#200 begin a = 8'hff; b = 8'h03; op = 4'b1000; end//逻辑右移

#200 begin a = 8'hff; b = 8'h03; op = 4'b1001; end//算数右移

#200 begin a = 8'hff; b = 8'h03; op = 4'b1010; end // 左移

#200 ;

end

endmodule 图3-6 用 Block Design 设计的 8 位运算器仿真波形

五、实验数据记录和处理

8 位运算器设计中的仿真文件alu8_verilog_sim.v:

`timescale 1ns / 1ps

module alu8_verilog_sim( );

// input

reg [7:0] a = 8'h16;

reg [7:0] b = 8'h12;

reg [3:0] op = 4'b0000; // 加法

//output

wire [7:0] res;

wire cf;

wire ovf;

wire sf;

wire zf;

// initial

alu8_verilog U (.a(a),.b(b),.op(op),.res(res),.cf(cf),

.ovf(ovf),.sf(sf),.zf(zf));

initial begin

#200 op = 4'b0001; // 减法

#200 begin a = 8'h7f; b = 8'h2; op = 4'b0000; end

#200 begin a = 8'hff; b = 8'h2; op = 4'b0000; end

#200 begin a = 8'h16; b = 8'h17; op = 4'b0001; end

#200 begin a = 8'hf0; b = 8'h0f; op = 4'b0100; end // 与

#200 begin a = 8'hf0; b = 8'h0f; op = 4'b0101; end // 或

#200 begin a = 8'hf0; b = 8'h0f; op = 4'b0110; end // 非

#200 begin a = 8'hff; b = 8'hff; op = 4'b0111; end // 异或

#200 begin a = 8'hff; b = 8'h03; op = 4'b1000; end//逻辑右移

#200 begin a = 8'hff; b = 8'h03; op = 4'b1001; end//算数右移

#200 begin a = 8'hff; b = 8'h03; op = 4'b1010; end // 左移

#200 ;

end

endmodule

用 Block Design 设计的 8 位运算器中使用的仿真文件alu8_bk_sim.v:

`timescale 1ns / 1ps

module alu8_bk_sim( );

// input

reg [7:0] a = 8'h16;

reg [7:0] b = 8'h12;

reg [3:0] op = 4'b0000; // 加法

//output

wire [7:0] res;

wire cf;

wire ovf;

wire sf;

wire zf;

// initial

alu8_bk U (.a(a),.b(b),.op(op),.res(res),.cf(cf),

.ovf(ovf),.sf(sf),.zf(zf));

initial begin

#200 op = 4'b0001; // 减法

#200 begin a = 8'h7f; b = 8'h2; op = 4'b0000; end

#200 begin a = 8'hff; b = 8'h2; op = 4'b0000; end

#200 begin a = 8'h16; b = 8'h17; op = 4'b0001; end

#200 begin a = 8'hf0; b = 8'h0f; op = 4'b0100; end // 与

#200 begin a = 8'hf0; b = 8'h0f; op = 4'b0101; end // 或

#200 begin a = 8'hf0; b = 8'h0f; op = 4'b0110; end // 非

#200 begin a = 8'hff; b = 8'hff; op = 4'b0111; end // 异或

#200 begin a = 8'hff; b = 8'h03; op = 4'b1000; end//逻辑右移

#200 begin a = 8'hff; b = 8'h03; op = 4'b1001; end//算数右移

#200 begin a = 8'hff; b = 8'h03; op = 4'b1010; end // 左移

#200 ;

end

endmodule

六、实验结果与分析 8 位运算器的设计仿真文件的运行结果: 图3-7 8位运算器仿真波形用 Block Design 设计的8位运算器中的仿真文件的运行结果: 图3-7 8位运算器仿真波形用 Block Design 设计的8位运算器中的仿真文件的运行结果:  图3-8 用 Block Design 设计的 8 位运算器仿真波形

七、讨论、心得

首先我在做实验的过程中深刻体会了计算机ALU的设计原理:对于所有不同的操作,操作数的输入端、输出端都是复用的,具体执行何种操作,是通过输入的op信号来决定的。在ALU外部使用的是op信号,但是在内部使用的是sel信号,这就需要使用卡诺图来进行两种信号的映射。本次实验是使用 Block Design 方式来设计 8 位运算器,通过实验,我对图形化设计的过程有了一定的了解,并成功设计了能进行算术运算(加、减法)、逻辑运算(与、或、非、异或)和移位运算(逻辑左移、算术左移、逻辑右移、算术右移)的 8 位运算器 图3-8 用 Block Design 设计的 8 位运算器仿真波形

七、讨论、心得

首先我在做实验的过程中深刻体会了计算机ALU的设计原理:对于所有不同的操作,操作数的输入端、输出端都是复用的,具体执行何种操作,是通过输入的op信号来决定的。在ALU外部使用的是op信号,但是在内部使用的是sel信号,这就需要使用卡诺图来进行两种信号的映射。本次实验是使用 Block Design 方式来设计 8 位运算器,通过实验,我对图形化设计的过程有了一定的了解,并成功设计了能进行算术运算(加、减法)、逻辑运算(与、或、非、异或)和移位运算(逻辑左移、算术左移、逻辑右移、算术右移)的 8 位运算器

|

【本文地址】