| SiC MOSFET 驱动与保护电路设计 | 您所在的位置:网站首页 › SSD2805驱动电路 › SiC MOSFET 驱动与保护电路设计 |

SiC MOSFET 驱动与保护电路设计

|

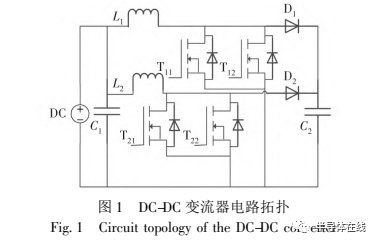

0 引言 SiC MOSFET 具有输入阻抗高、高频性能好、单个驱动功率小和无需并联均流控制等显著优势。随着 SiC MOSFET 的发展和成熟,变流产品向着高频、高功率密度、高可靠性的方向快速发展。在 DC-DC 变流器研发过程中,研究人员也对SiC MOSFET 的应用进行了积极探索。目前国内外SiC MOSFET 的驱动电路多设计为简单的隔离驱动电路,该电路只是驱动 SiC MOSFET 开关,但在异常工作情况下不能有效保护 SiC MOSFET,容易导致其损坏,而且由于单个 SiC MOSFET 散热面积较小,且相同电压等级的 SiC MOSFET 电流越大,成本要高得多,为了提高 SiC MOSFET 驱动电路的可靠性及驱动能力,本文研究了基于 ACPL-355JC光耦驱动模块的并联 SiC MOSFET 驱动和保护电路,该设计方案不仅使驱动系统的可靠性大大提高,而且增加了多种驱动保护电路来提高产品的稳定性。 SiC MOSFET 固有的输出寄生电容以及电路中寄生电感和寄生电阻等参数的存在,会引起 SiCMOSFET 在高速开关过程中产生过电压和振荡等问题,针对该问题本文还提出了一种 RC 吸收电路的计算设计方法。 1 DC-DC变流器电气拓扑 基于交错升压电路的 DC-DC 变流器如图 1 所示。交错升压 DC-DC 电路采用相位差 180°的两路脉冲宽度调制 ( PWM) 信号控制 SiC MOSFET 的通断。为了增大每一路功率器件的散热面积,每一路 DC-DC 采用并联的两个小电流 SiC MOSFET 代替单个大电流的 SiC MOSFET,SiC MOSFET 的型号为 C3M0075120J。  2 SiC MOSFET 驱动电路设计 2. 1 驱动电路设计基本要求 SiC MOSFET 对驱动电路的基本要求主要有:①驱动电流要足够大,以缩短米勒平台的持续时间使驱动脉冲前后沿足够陡峭,尤其在多管并联的工况下; ②驱动回路的驱动电阻要小,导通时能够快速对栅极电容充电,关断时栅极电容能够快速放电,以加快 SiC MOSFET 的开关响应速度; ③为了保证 SiC MOSFET 可靠触发导通,栅极驱动电压应高于器件的开启电压; ④驱动电路采用负压关断,防止误导通,增强其抗干扰能力; ⑤需具有小的寄生电感,减小系统的振荡; ⑥为了保证控制电路的正常运行,驱动电路和功率电路之间要有隔离; ⑦需具有必要的驱动保护电路。 2. 2 驱动电路原理 本文基于 ACPL- 355JC 光耦驱动模块设计了SiC MOSFET 驱动和保护电路,该电路由输入驱动信号调理电路、驱动保护电路和故障反馈电路等三部分构成。输入驱动信号调理电路对脉冲使能信号等进行缓冲、整形处理,来提高输入驱动信号的质量; 驱动保护电路对输入驱动信号进行放大,来驱动 SiC MOSFET 的导通与关断以及在 SiC MOSFET发生短路过流、驱动电源欠压等故障时起保护作用; 故障反馈电路将驱动保护电路的故障结果反馈给控制电路。驱动电路原理如图 2 所示。ACPL-355JC 为光耦隔离驱动模块,具有最大 2 262 V 的工作绝缘电压,能完美实现功率电路和驱动电路的电气隔离功能; 最高开关频率可达 1 MHz,最大传输延迟时间只有 150 ns,能够满足 SiC MOSFET 高频通断的要求。ACPL-355JC 有两个故障报告机制,即正输出电源电压 ( VDD2) 的欠压保护 ( UVLO) 和过流保护 ( FAULT) ,UVLO 故障优先级最高,FAULT 故障次之。在过电流故障条件下,通过 SS 引脚软关断,关断速率可以通过电阻 R51调整。最大 10 A 的驱动峰值电流足以同时驱动两个并联的 SiC MOSFET。  2. 3 驱动电阻 ( RG) 设计 RG的大小对 SiC MOSFET 开关速度、电压尖峰、开关过程的振荡以及系统效率都有较大的影响,合适的 RG对于系统整体性能具有至关重要的影响。实验前需要通过理论计算选择一个较合适的RG值。首先,SiC MOSFET 和 RG可以认为是一个简单的 RC 电 路,电 压 由 ACPL - 355JC 提 供。根 据ACPL-355JC的正、负输出电源电压 ( VDD2和 VSS2)以及最大驱动峰值电流 ( IO,PEAK= 10 A) 来计算 RG最小值 ( RG,MIN) ,即  式中 ROUT,MIN为 ACPL-355JC 内部的最小栅极输出电阻。根据式 ( 1) 可以求得 RG,MIN= 1. 6 Ω。RG和 ROUT,MIN将确保输出电流不会超过 ACPL-355JC 的绝对最大额定值 10 A。其 次,根 据ACPL-355JC 的最大输出驱动功率 ( PO,MAX) 来计算 RG。ACPL-355JC 实际输出驱动功率 ( PO) 计算公式为  式中: PO,BIAS为输出保持功率; PO,SWITCHING为驱动开关功率; PHS和 PLS分别为驱动导通和关断功率;IDD2为 ACPL - 355JC 的 工 作 电 流; QG 为 SiC MOSFET 的 栅 极 电 荷; f 为 驱 动 开 关 频 率;ROUTN,MAX和 ROUTP,MAX分别为 ACPL-355JC 的最大栅极关断和导通输出电阻。由式 ( 2) ~ ( 4) 可以求得 PO≈170 mW。因为两个并联 SiC MOSFET 的输出驱动功率为2PO≈340 mW,小于 PO,MAX= 600 mW,所以选择RG= 2. 5 Ω,此时 ACPL-355JC 能够驱动两个并联的 SiC MOSFET。 2. 4 输出短路保护设计 SiC MOSFET 的晶圆面积小于 IGBT 的晶圆面积,其散热能力比 IGBT 差,一般 SiC MOSFET 发生短 路 故 障 后 要 求 2 μs 内 关 断 脉 冲 信 号。ACPL-355JC通 过 检 测 SiC MOSFET 的 导 通 压 降( VDS) 是否超过内部设置的比较器阈值电压进行短路保护,其工作原理如图 3 所示。  ACPL-355JC 内部设置的比较器阈值电压为9 V。当 SiC MOSFET 发生短路故障时,VDS大 于9 V时,消隐电容充电电流 ( ICHG) 给 消 隐 电 容( CBLANK) 充电,当 ACPL - 355JC OC 引脚的电压( VOC) 大于 9 V 时,触发 ACPL-355JC 的保护动作。通 过 设 置 CBLANK的值来设定消隐时间( tBLANK) ,即  式中: tOC,BLANKING为内部消隐时间; VOC,INITIAL为 SiC MOSFET 正常导通时 ACPL-355JC 驱动模块 OC 引脚的电压值; ICHG= 1 mA。当 SiC MOSFET 正常导通时,恒流源 ICHG通过电阻 ( RBLOCK) 、二极管 ( DBLOCK) 和 SiC MOSFET进行释放。其 中,DBLOCK选择高压快恢复二极管( US1M) ,其反向耐压为 1 000 V,导通压降 ( VF )为 1. 7 V。根据 SiC MOSFET ( C3M0075120J) 的手册,正常工作时 SiC MOSFET 的导通压降为 1 V。在保证 SiC MOSFET 正常导通时 VOC远低于比较器阈值电压 9 V 的前提下, RBLOCK选择为 1 kΩ,则正常导通时VOC,INITIAL为  由式 ( 6) 可以求得 VOC,INITIAL= 3. 7 V。当图 1 中升压电感发生退饱和等故障导致电感值突减时,SiC MOSFET 会发生短路故障,导致流过SiC MOSFET 的电流迅速增加,此时应该保证 2 μs内触发 ACPL-355JC 的保护功能以关断脉冲信号。CBLANK用于设置 tBLANK,tOC,BLANKING= 0. 4 μs。根据式( 5) 计 算 出 CBLANK< 302 pF。实 际 选 择 CBLANK=220 pF,发生短路故障时理论保护时间为 1. 566 μs。 2. 5 RC吸收电路设计 本文提出了一种 SiC MOSFET 的漏源极之间充放电型 RC 吸收电路参数的计算方法。首先根据波形的振荡频率来计算电路中总的寄生电容值 ( C)和寄生电感值 ( L) ,然后再计算出 RC 吸收电路的电阻值 ( RSN) 和电容值 ( CSN) ,RC 吸收电路原理如图 4 所示。  RSN和 CSN的具体计算过程如下。①首先根据SiC MOSFET 的 DS 引脚之间的电压 ( UDS) 波形振荡周期计算出谐振频率 ( f0) ,如图 5 所示。②在图 4 中 SiC MOSFET 的漏源极之间接一个外接电容( Ctest) ,由此再测算出一个谐振频率 ( f1) 。③计算出 C 和 L,即  ④根据 C 和 L 计算出阻尼因数,且选择阻尼因数取 1 时为最佳来计算 RSN,即  ⑤根据经验一般选取CSN= 3C。  3.实验验证 本文基于以上设计搭建一台 SiC MOSFET 双并联交错升压 DC-DC 变流器的样机,主电路如图 1所示,样机如图 6 所示。样机基于 TMS320F28335 DSP 芯片设计的控制系统; 主电路由直流支撑电容、储能电感和 SiC MOSFET 等构成,样机输入电压为 DC 72 V,母线电压为 DC 570 V,额定输出功率为 3 kW,母线电压支撑电容为 560 μF,储能电感为 75 μH,开关频率为 80 kHz。  采用上述实验平台对 RC 吸收电路计算方法的有效性进行验证,增加 RC 吸收电路前后 SiC MOSFET 的DS 引脚之间电压和母线电压 ( UDC) 的实验波形如图 7 所示。图 7 表明,增加 RC 吸收电路后,电压过冲由1 080 V下降至 740 V,降低了约31%; 没有 RC 吸收电路时 SiC MOSFET 的 UDS单个波形 振 荡 周 期 为 51 ns,经 过 10 个 振 荡 周 期( 510 ns) 后波形振荡基本消失,增加 RC 吸收电路后无明显振荡周期,且213 ns后波形振荡基本消失。实验验证了增加 RC 吸收电路后不仅有效降低了电压过冲和振荡,而且减小了 SiC MOSFET 开关过程中母线电压的波动。  4 结论 本文对基于 ACPL- 355JC 的 SiC MOSFET 驱动电路的设计进行了详细分析,提出了一种 RC吸收电路参数的计算方法,并通过实验验证了该RC 吸收电路的有效性,也间接验证了该驱动电路的可行性。所设计的驱动保护电路和 RC 吸收电路已经应用于铁路上的应急通风逆变器,而且通过了实际运行考核。后续将在降低吸收电路功率损耗和提高驱动保护电路稳定性等方面进行更加深入的研究。 来源:集成电路设计与应用 作者:咸粤飞、崔晓光、胡冰、邵春伟、赵栋、赵振华、闫青亮( 中车青岛四方车辆研究所有限公司) |

【本文地址】