| 如何通过Codewarrior QCVS工具生成DDR4颗粒时序配置参数 – Lijiandong' Blog | 您所在的位置:网站首页 › D9LHT颗粒参数 › 如何通过Codewarrior QCVS工具生成DDR4颗粒时序配置参数 – Lijiandong' Blog |

如何通过Codewarrior QCVS工具生成DDR4颗粒时序配置参数 – Lijiandong' Blog

|

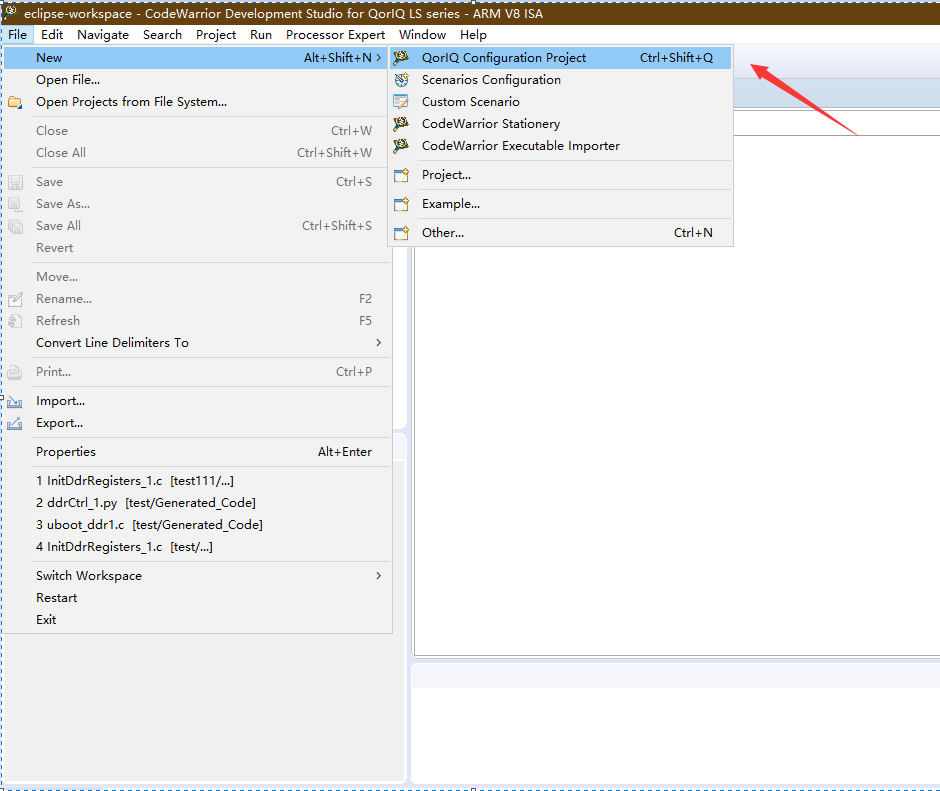

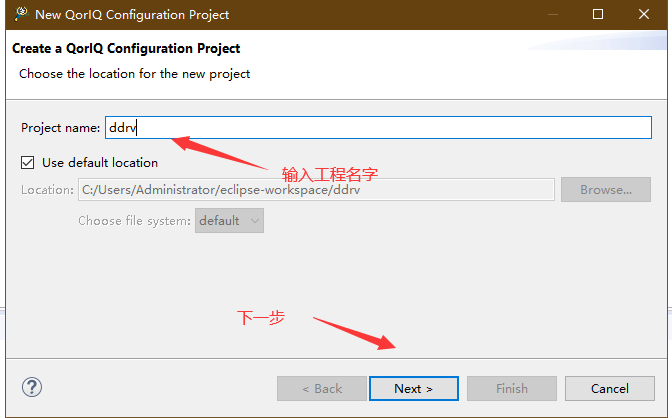

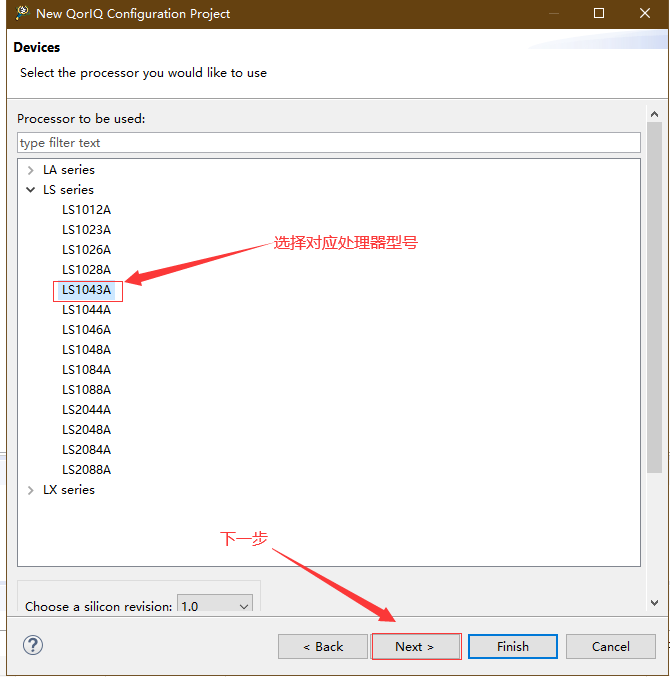

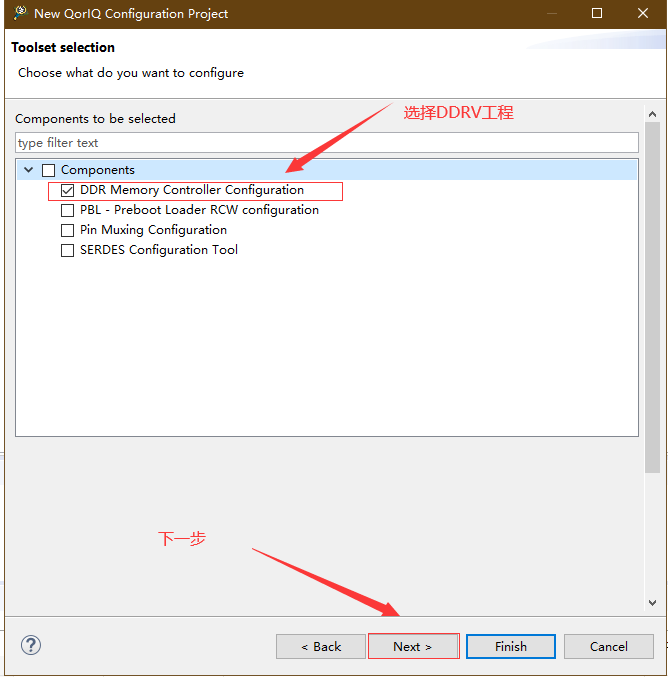

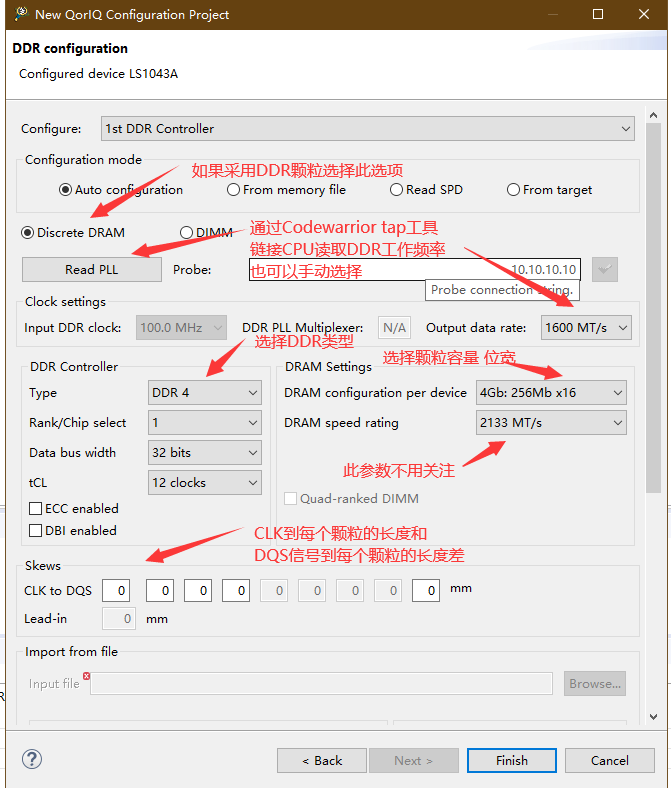

1.新建工程

2

3

4

5 通过手动选择的DDR工作频率一定要跟RCW配置的工作频率一样。

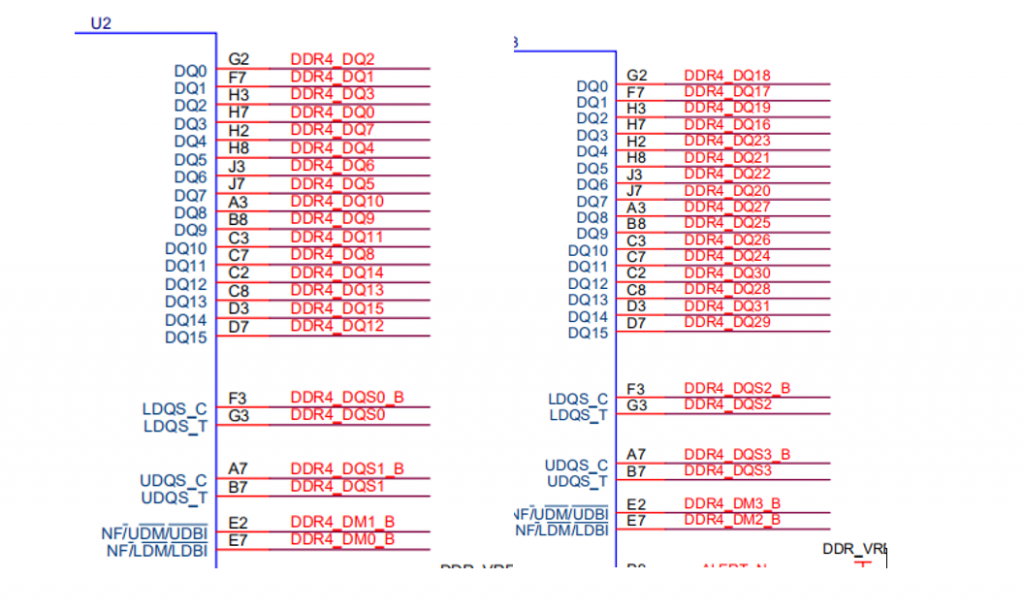

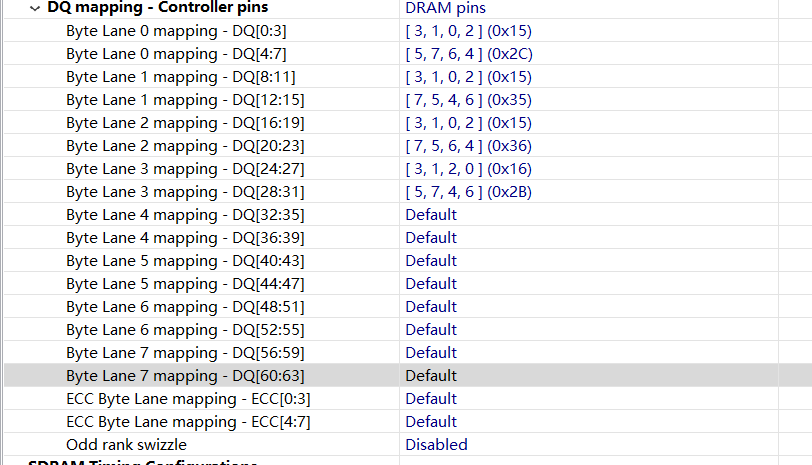

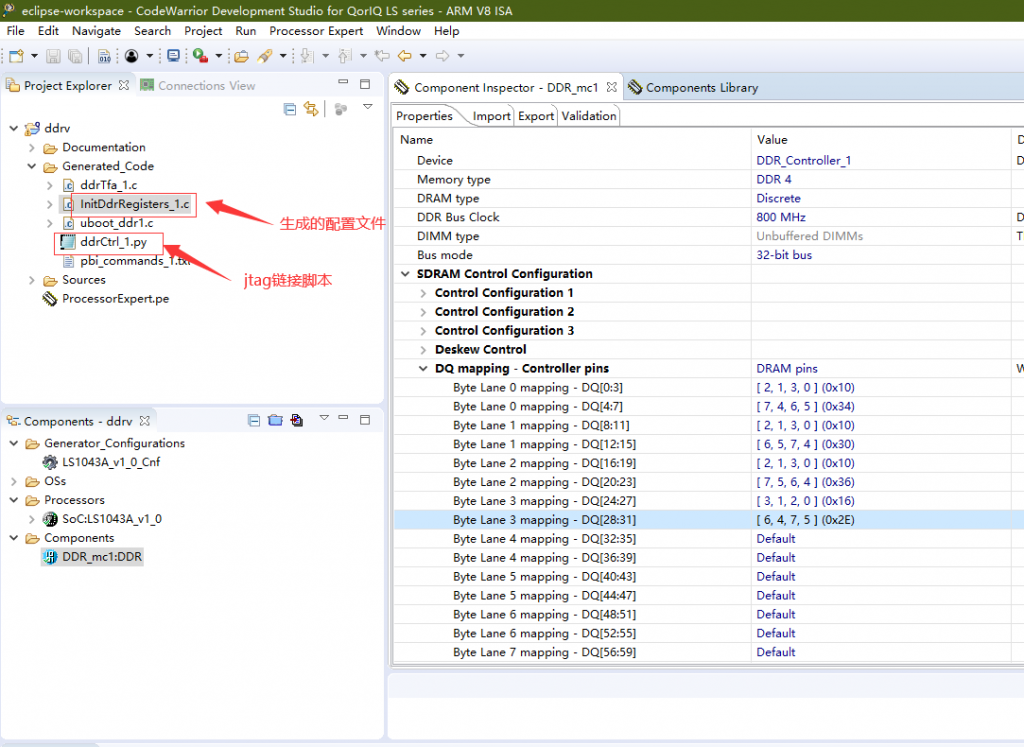

6 根据PCB布线配置DQ Mapping,如下是DDR4颗粒侧数据线布线调整样例.

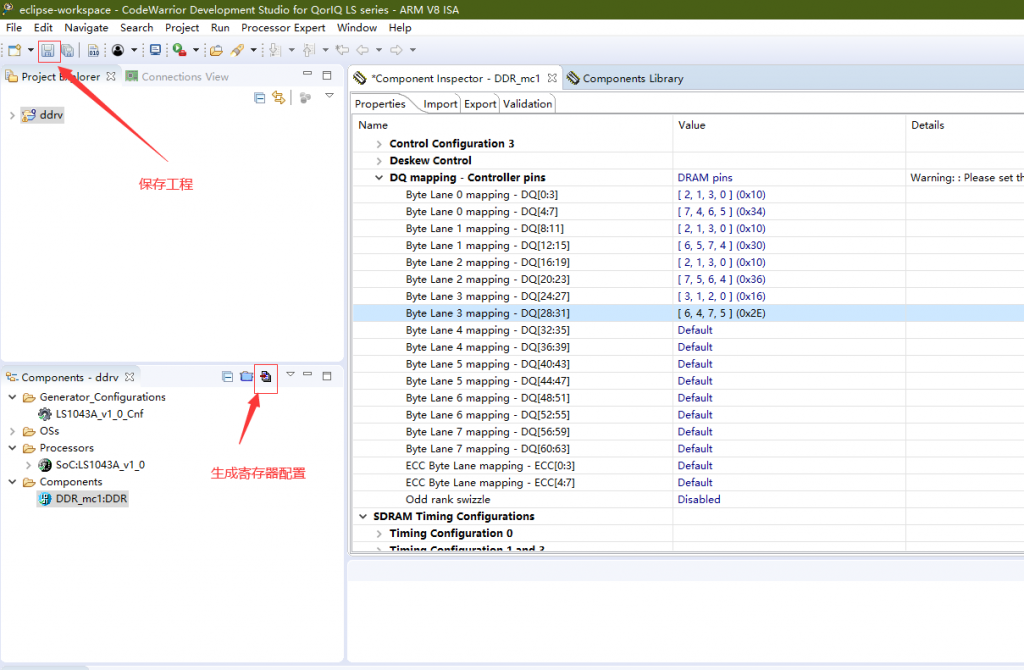

7 根据上图颗粒侧数据线调整样例,配置DDR控制器的dq_mapping配置,LS1043 DDR4是32位数据总线

8 保存工程,生成配置文件

9

9 更新到atf里,修改如下文件: 打开CONFIG_STATIC_DDR这个宏 修改/packages/firmware/atf/plat/nxp/soc-ls1043/ls1043ardb/platform.mk, CONFIG_STATIC_DDR := 1 /packages/firmware/atf/plat/nxp/soc-ls1043/ls1043ardb/ddr_init.c Discrete DDR support When a board design uses fixed or discrete DDR, a flag named CONFIG_STATIC_DDR needs to be defined in platform_def.h file to enable discrete DDR timings. The below function (board_static_ddr) will also need to be defined in a board specific file. This function uses the structure ddr_cfg_regs which is populated with specific DDR register configurations. For Example, the static_1600 structure shown below is used for 1600MT/s. const struct ddr_cfg_regs static_1600 = { .cs[0].config = 0x80010412, .cs[0].bnds = 0x7F, .cs[1].config = 0x0202, .cs[1].bnds = 0x008000BF, .sdram_cfg[0] = 0XC52C0000, .sdram_cfg[1] = 0x00401010, .sdram_cfg[2] = 0x0, .timing_cfg[0] = 0xFF55000C, .timing_cfg[1] = 0xCEC60C42, .timing_cfg[2] = 0x0048D11C, .timing_cfg[3] = 0x01111000, .timing_cfg[4] = 0xD501, .timing_cfg[5] = 0x05401400, .timing_cfg[6] = 0x0, .timing_cfg[7] = 0x23300000, .timing_cfg[8] = 0x03114600, .timing_cfg[9] = 0x0, .dq_map[0] = 0x56C57554, .dq_map[1] = 0xD96AC000, .dq_map[2] = 0x0, .dq_map[3] = 0x0, .sdram_mode[0] = 0x01010214, .sdram_mode[1] = 0x0, .sdram_mode[9] = 0x04800000, .sdram_mode[8] = 0x400, .sdram_mode[2] = 0x0, .sdram_mode[3] = 0x0, .sdram_mode[10] = 0x0, .sdram_mode[11] = 0x0, .sdram_mode[4] = 0x0, .sdram_mode[5] = 0x0, .sdram_mode[12] = 0x0, .sdram_mode[13] = 0x0, .sdram_mode[6] = 0x0, .sdram_mode[7] = 0x0, .sdram_mode[14] = 0x0, .sdram_mode[15] = 0x0, .interval = 0x18600618, .zq_cntl = 0x8A090705, .ddr_sr_cntr = 0x0, .clk_cntl = 0x2800000, .cdr[0] = 0x80040000, .cdr[1] = 0xa181, .wrlvl_cntl[0] = 0x86750606, .wrlvl_cntl[1] = 0x06060600, .wrlvl_cntl[2] = 0x00000000, }; |

【本文地址】