| 74ls151应用电路图大全(全加器\表决器) | 您所在的位置:网站首页 › 74ls151功能和引脚图 › 74ls151应用电路图大全(全加器\表决器) |

74ls151应用电路图大全(全加器\表决器)

|

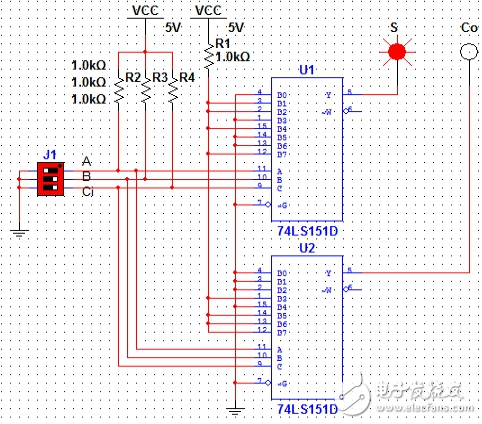

74ls151应用电路图(一):全加器设计电路

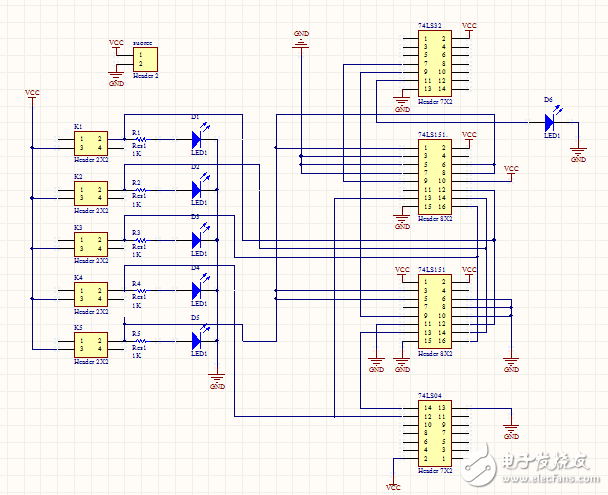

利用74LS151数据选择器可以设计如图6所示电路: 两个74LS151分别得到S和Co;其中U1的数据端配置为D1=D2=D4=D7=1,其余为0; U2配置为D3=D5=D6=D7=1,其余为0.

图6 同样,下面也给出{A=1,B=0,Ci=0};{A=0,B=1,Ci=0};{A=1,B=1,Ci=0}和{A=1,B=1,Ci=1}四种输入状态下的S和Co状态。

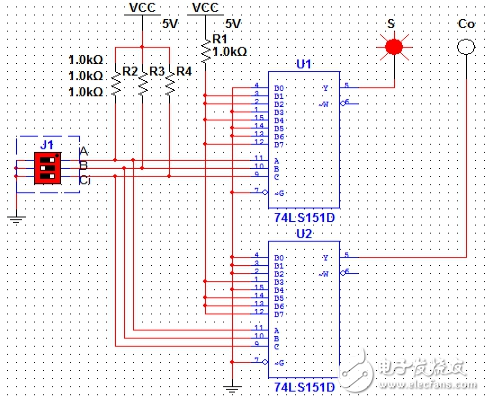

图7(A=1,B=0,Ci=0)

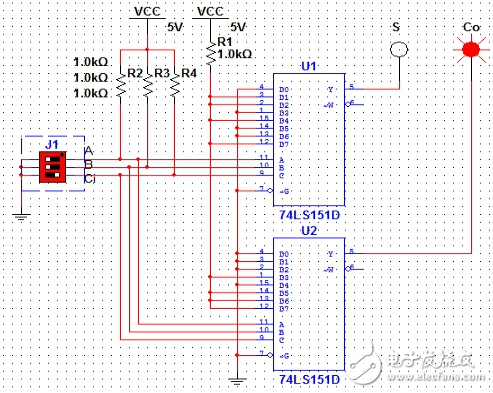

图8(A=0,B=1,Ci=0)

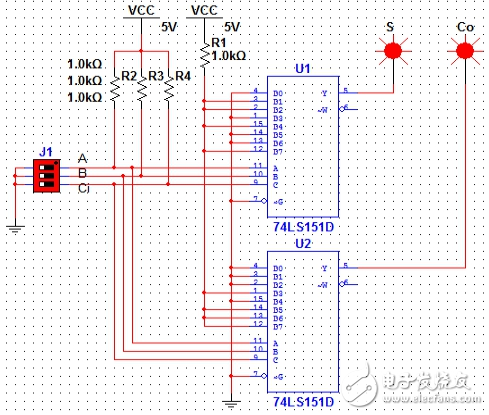

图9(A=1,B=1,Ci=0)

图10(A=1,B=1,Ci=1) 可以看出,电路的逻辑关系也是正确的。 74ls151应用电路图(二):实现三人表决器

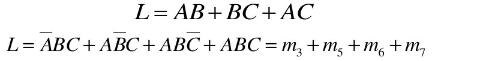

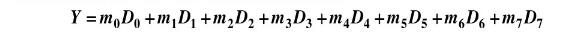

将输入变量接至数据选择器的地址输入端,即A=Ay,B=A,C=A。o输出变量接至数据选择器的输出端,即L=Y。将逻辑函数L的最小项表达式与74151的功能表相比较,

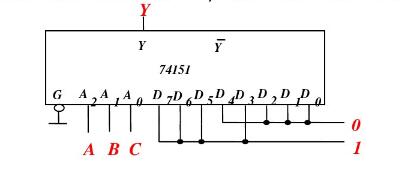

显然,Y式中出现的最小项,对应的数据输入端应接1,Y式中没出现的最小项,对应的数据输入端应接0。即D3=D5=D6=D7=1;D0=D1=D2=D4=0。

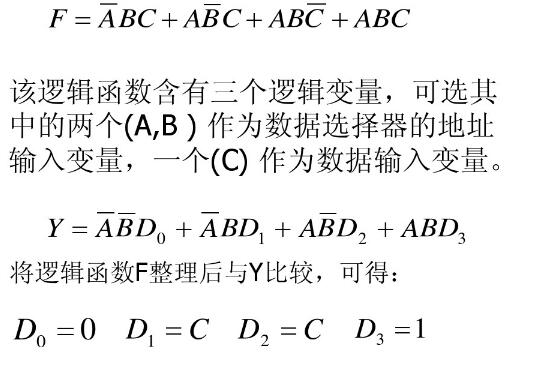

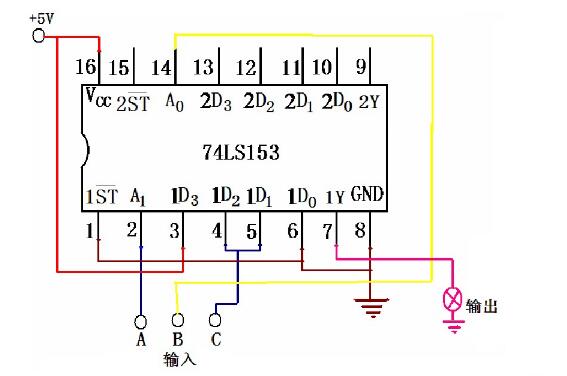

该逻辑函数含有三个逻辑变量,可选其中的两个(A,B)作为数据选择器的地址输入变量,一个(C)作为数据输入变量。 用数据选择器74LS151实现接线图

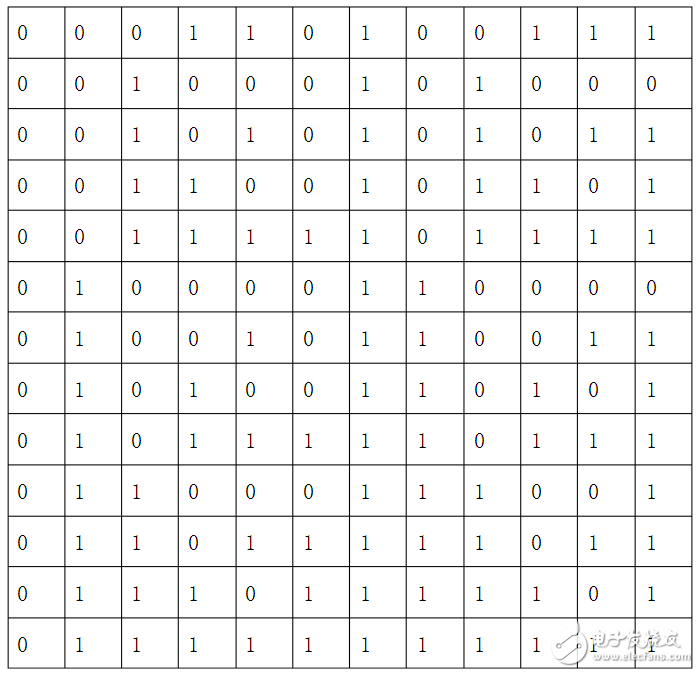

系统原理 五人表决器,只要赞成人数大于或等于三,则表决通过。因此,只需将每位表决人的结果相加,判断结果值。设五个开关A、B、C、D、E作为表决器的五个输入变量,输入变量为逻辑“1”时,表示表决者“赞成”,红灯亮;输入变量为“0”时,表示表决者“不赞成”,红灯不亮;输出逻辑“1”时,表示表决“通过”,绿灯亮;输出逻辑“0”时,表示表决“不通过”,绿灯不亮;当表决器的五个输入变量中有3个以上(含3个)为“1”时,则表决器输出为“1”,此时绿灯就亮了。 真值表

如果绿灯亮了,则表示表决通过,若绿灯不亮了,表示不通过。 电路设计

|

【本文地址】