| 74LS73双JK触发器引脚图 | 您所在的位置:网站首页 › 74HC273D触发器 › 74LS73双JK触发器引脚图 |

74LS73双JK触发器引脚图

|

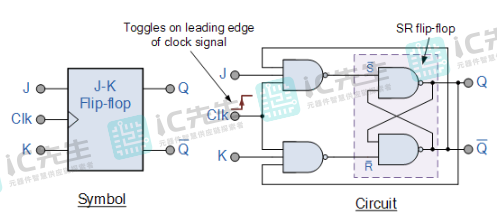

触发器和锁存器是用于存储单个位的小型设备,单个触发器代表两种状态,其中存储数据用1表示,另一个用0表示。SR锁存器有两个问题。在SR锁存器中,系统应避免S=R=0;另一个问题是当使能引脚为高电平时,可能不会发生正确的锁存问题。 为了解决这个问题,使用了JK触发器。JK触发器有一个内部SR锁存电路,但它也安装了一个时钟。时钟解决了这两个问题。JK触发器是以设计师Jack Kilby的名字命名的。JK触发器时钟还提供了一些额外的功能。它提供了四种输入组合,分别是逻辑1、逻辑0、无变化和切换。在本文中,小编介绍一种应用比较广泛的双JK触发器——74LS73。

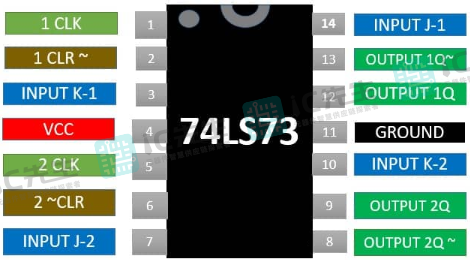

74LS73是一款双JK触发器,每当我们同时需要两个JK触发器时,该芯片就是最佳选择。74LS73内部有两个JK触发器,两者都有不同的结构,并且甚至不依赖对方或任何东西。 在74LS73器件中,用户甚至可以使用单个触发器而不使用另一个触发器。由于拥有众多的优良特性,74LS73在行业内被广泛应用。

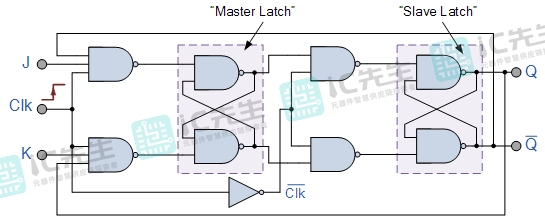

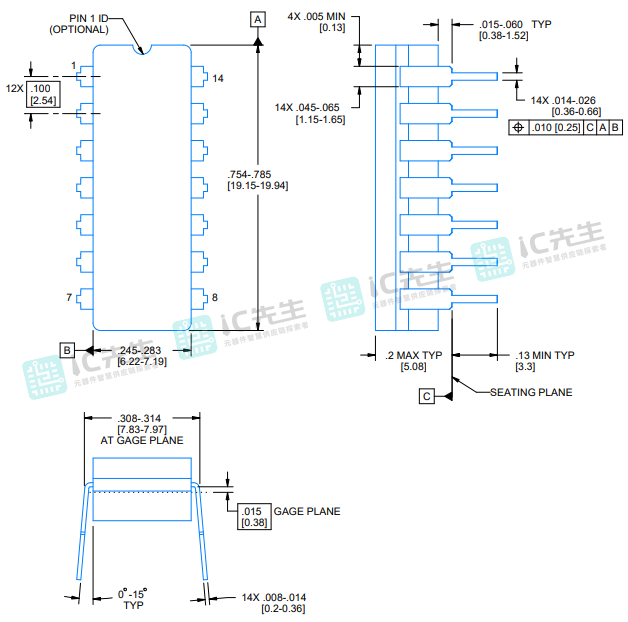

名称 引脚 功能描述 1 CLK 引脚1 第一个JK触发器的时钟引脚,利用脉冲的变化来改变状态。 1CLR (BAR) 引脚2 用作第一个触发器的重发引脚,低脉冲将用于清除触发器中的数据。 INPUT K-1 引脚3 用于将位发送到JK触发器的输入引脚。 VCC 引脚4 VCC用于给整个IC提供JK触发器的电源。 2CLK 引脚5 用于为74LS73中的第二个JK触发器提供时钟,脉冲从低电平到高电平的变化用于改变状态。 2CLR (bar) 引脚6 用作第二个JK触发器的复位引脚,低脉冲将用于重置触发器中的数据。 INPUT J-2 引脚7 用于发送JK触发器的第二个输入。 OUTPUT 2Q (bar) 引脚8 用作第二个JK触发器的反相输出。 OUTPUT 2Q 引脚9 用作第二个JK触发器的非反相输出。 INPUT K-2 引脚10 用作第二个JK触发器的输入引脚。 GROUND 引脚11 接地引脚用于提供电源地以及与IC的另一个电路的公共地。 OUTPUT 1Q 针脚12 提供第一个JK触发器的非反相输出。 OUTPUT 1Q (bar) 针脚13 提供第一个JK触发器的反相输出。 INPUT J-1 针脚14 用作第一个J触发器的第二个输入。 工作原理 要了解74LS73,首先需要了解SR锁存器。SR锁存器有两个输入。第一个是重置,第二个称为设置。至少一个引脚的输出应为高电平,而另一个引脚应为低电平状态。SR锁存器工作有四种逻辑状态,即当两个输入引脚上有不同的输入但有相同的输出时,在0,0的情况下,输出变为无效,在1,1的情况下,输出变得不可预测。因此,为了解决JK触发器中的这个问题,安装了一个内部时钟,时钟控制输出随输入状态的变化。 JK触发器配有两个SR锁存器和四个NAND门,如下图所示。第一个锁存器用作主锁存器,另一个SR锁存器用作从锁存器。两个NAND门和从SR锁存器向主SR锁存器提供输入。从锁存器到主锁器的输出有助于JK触发器进行切换脉冲。主锁存器的输入信号连接到与非门。与非门的输出已连接到另一个引脚,即时钟引脚。

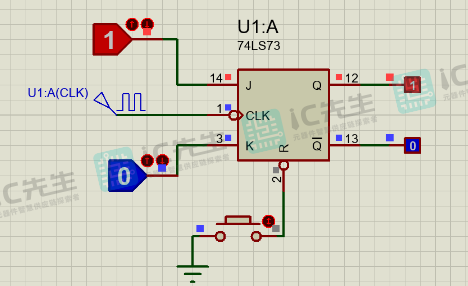

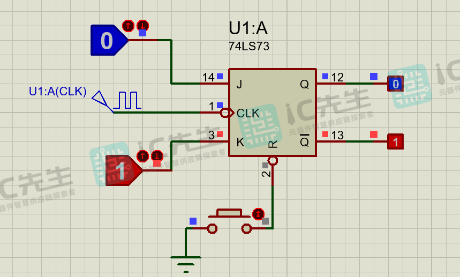

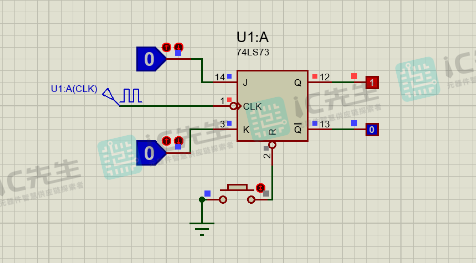

时钟引脚仅允许NAND门在Clock获得上升脉冲时将输出提供给主机。当时钟为LOW时,将没有输出。在LOW Pulse(低脉冲)的情况下,输出将被忽略。当从锁存器的输入门将有HIGH到LOW脉冲时,主锁存器输出将被提供给从。主控器和从控器之间的这种时钟过程使触发器利用定时信号将数据从主控器传输到从控器。 真值表以下输出将根据给定的输入完成。 时钟脉冲 输入 输入 输出 输出 结果 CLK J K Q Q’ – X 0 0 1 0 无变化 X 0 0 0 1 无变化 L–H 0 1 1 0 与SR锁存器相同 X 0 1 0 1 与SR锁存器相同 L–H 1 0 0 1 与SR锁存器相同 X 1 0 1 0 与SR锁存器相同 L–H 1 1 0 1 切换(Toggle) L–H 1 1 1 0 切换(Toggle) L–H=低到高脉冲 X=脉冲无变化 Proteus示例电路 在Proteus中,当我们在J上给出逻辑1状态,在K上给出0状态时,我们会在Q上收到1,在Q'上收到0,当我们在J上发送0,在K上发送1时,我们会在Q'上收到 1,在Q上收到0。整个过程将遵循上面提到的真值表。时钟脉冲随时间不断变化以改变输出。 现在来了解另外两种状态。在“J”处应用高逻辑,然后可能会注意到Q变为1,但是当你尝试更改“J”处的逻辑时,它不会受到影响。因为这表明触发器中已经存储了一位。要删除存储的位,只需使用重置按钮即可。

在数字设备中,可以通过数字方式完成此重置功能。重置按钮将从所有输出引脚清除该位,但如果我们使用另一种方法,例如将“J”转为低电平,将“K”转为高电平,则位将从Q移位到Q'。这种转变不是从Q到Q',而是来自K。

接下来将讨论最后一个状态,它是两个输入的一个状态。当我们在两个输入上应用一个时,输出上的一个将会切换。输出将不稳定。它会随着输入时钟信号的速度而不断变化。这四种效果描述了触发器如何存储数据并避免从触发器发送无效数据。

74LS73是一种集成电路(IC)芯片,它是一款双JK触发器,通常用于构建计数器、时序逻辑和其它数字逻辑电路。该芯片集成了两个独立的JK触发器,每个触发器都有两个数据输入(J和K)以及时钟输入(CLK)和异步清零输入(CLR)。 74LS73每个JK触发器都可以通过时钟输入(CLK)来控制,在时钟信号的上升沿或下降沿,触发器会根据J和K输入的状态来改变其输出。此外,它还具有异步清零功能,当CLR输入为低电平时,可以立即将触发器的状态清零。 74LS73每个JK触发器都有两个输出:Q和Q'。它们表示触发器的状态,可以用于构建各种数字逻辑功能。74LS73通常用于构建二进制计数器、频率分频器、状态机和其它与时序和计数有关的数字电路。 |

【本文地址】